CD4027BC

Description

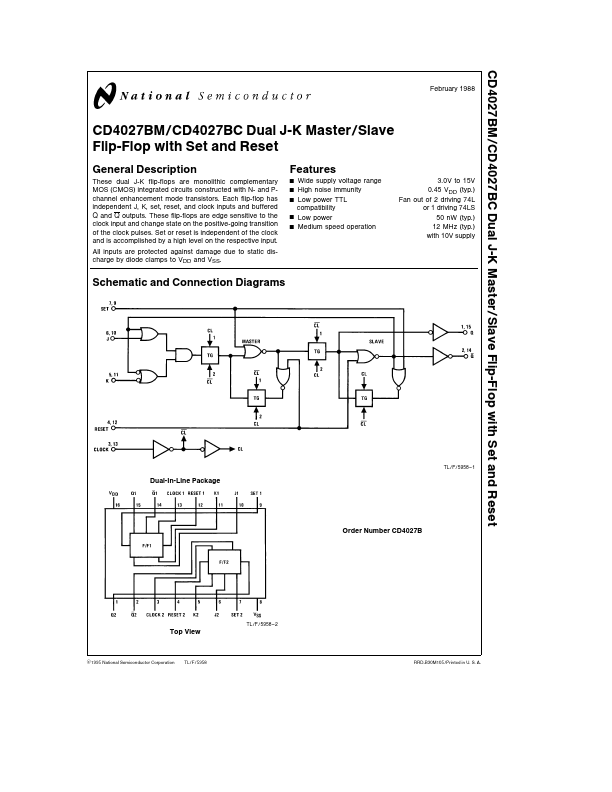

These dual J-K flip-flops are monolithic plementary MOS (CMOS) integrated circuits constructed with N- and Pchannel enhancement mode transistors Each flip-flop has independent J K set reset and clock inputs and buffered Q and Q outputs These flip-flops are edge sensitive to the clock input and change state on the positive-going transition of the clock pulses Set or reset is independent of the clock and is acplished by a high level on the respective input All inputs are protected against damage due to static discharge by diode clamps to VDD and VSS.