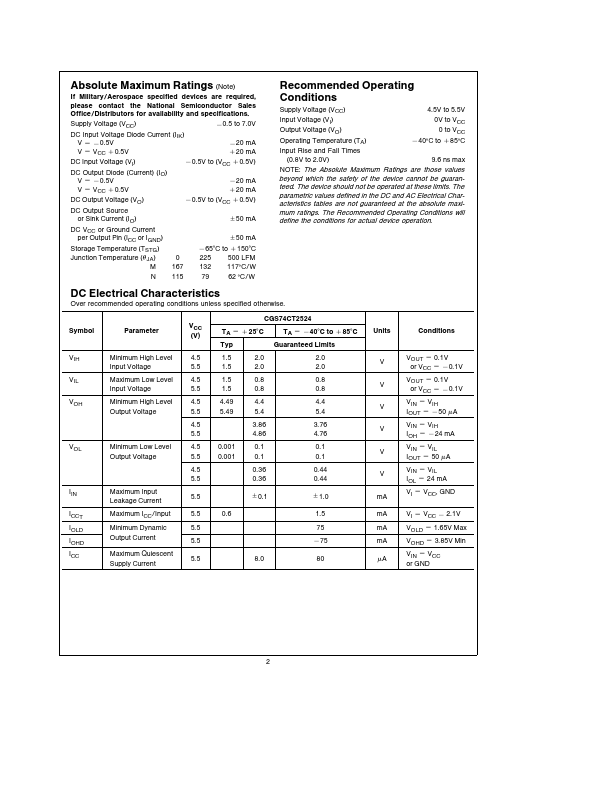

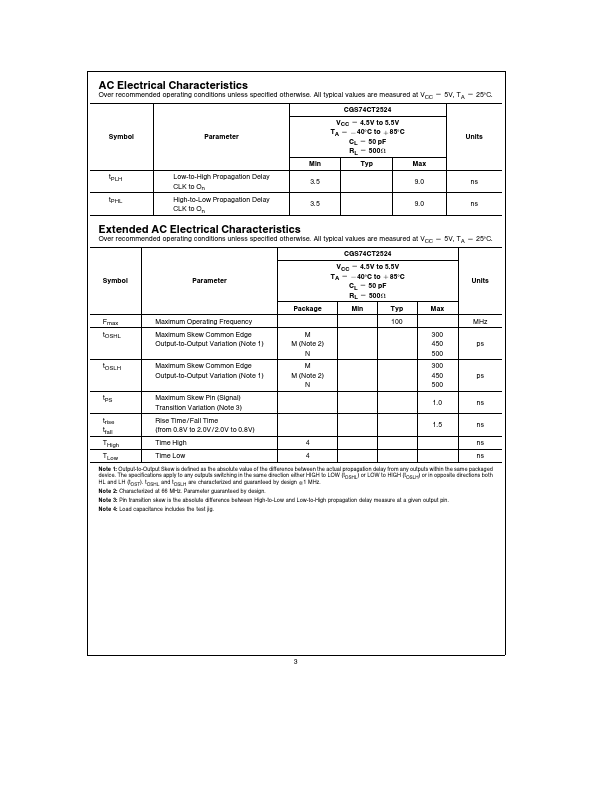

Datasheet Summary

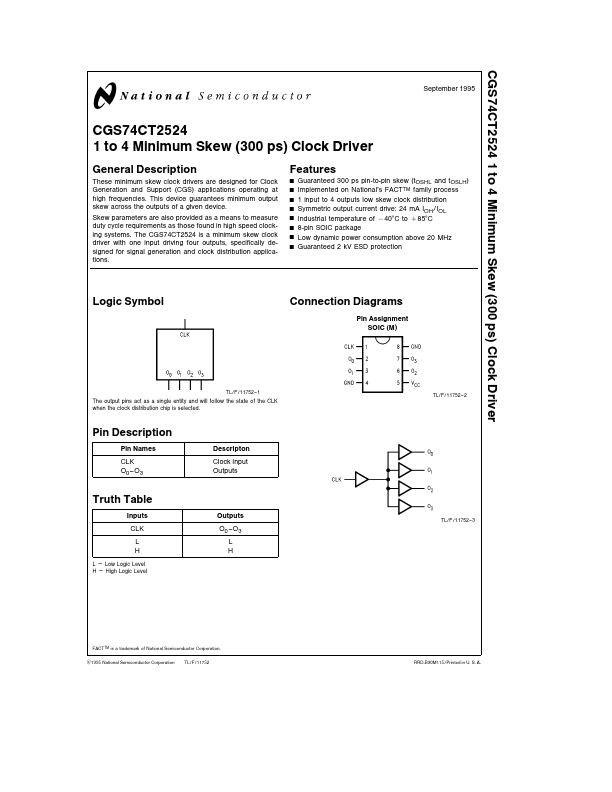

CGS74CT2524 1 to 4 Minimum Skew (300 ps) Clock Driver

September 1995

CGS74CT2524 1 to 4 Minimum Skew (300 ps) Clock Driver

General Description

These minimum skew clock drivers are designed for Clock Generation and Support (CGS) applications operating at high frequencies This device guarantees minimum output skew across the outputs of a given device Skew parameters are also provided as a means to measure duty cycle requirements as those found in high speed clocking systems The CGS74CT2524 is a minimum skew clock driver with one input driving four outputs specifically designed for signal generation and clock distribution applications

Features

Y Y Y Y Y Y Y Y

Guaranteed 300 ps pin-to-pin...