Description

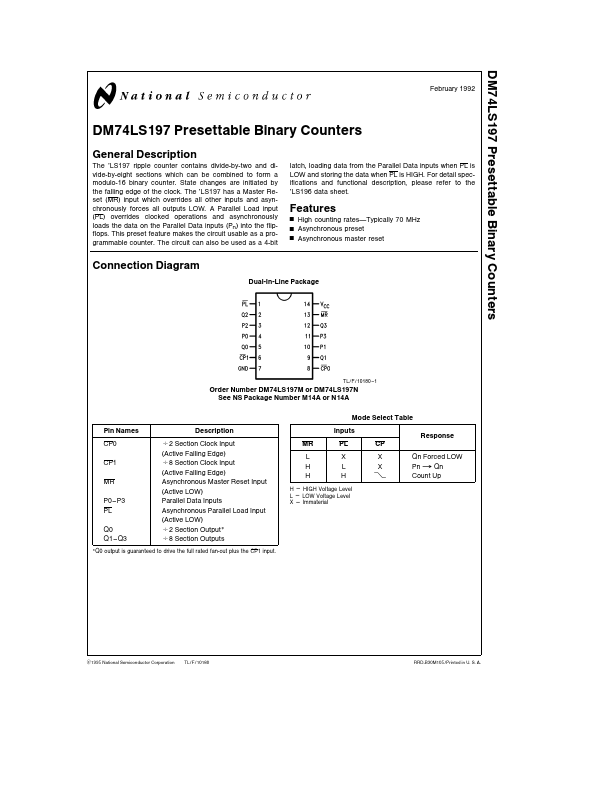

The ’LS197 ripple counter contains divide-by-two and divide-by-eight sections which can be bined to form a modulo-16 binary counter State changes are initiated by the falling edge of the clock The ’LS197 has a Master Reset (MR) input which overrides all other inputs and asynchronously forces all outputs LOW A Parallel Load input (PL) overrides clocked operations and asynchronously loads the data on the Parallel Data inputs (Pn) into the flipflops This preset feature makes the circuit usable as a programmable counter The circuit can also be used as a 4-bit latch loading data from the Parallel Data inputs when PL is LOW and storing the data when PL is HIGH For detail specifications and functional description please refer to the ’LS196 data sheet.