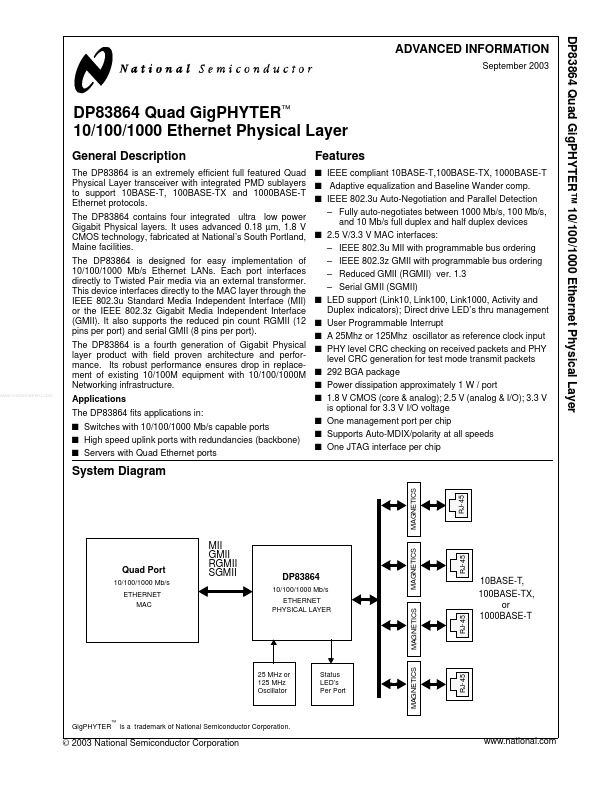

DP83864 Overview

Key Specifications

Key Features

- IEEE compliant 10BASE-T,100BASE-TX, 1000BASE-T Physical Layer transceiver with integrated PMD sublayers

- Adaptive equalization and Baseline Wander comp. to support 10BASE-T, 100BASE-TX and 1000BASE-T

- User Programmable Interrupt pins per port) and serial GMII (8 pins per port)

- A 25Mhz or 125Mhz oscillator as reference clock input The DP83864 is a fourth generation of Gigabit Physical