DP8403

DP8403 is Error Detection and Correction Circuits manufactured by National Semiconductor.

- Part of the DP8402A comparator family.

- Part of the DP8402A comparator family.

DP8402A DP8403 DP8404 DP8405 32-Bit Parallel Error Detection and Correction Circuits (EDAC’s)

Obsolete

PRELIMINARY

August 1989

DP8402A DP8403 DP8404 DP8405 32-Bit Parallel Error Detection and Correction Circuits (EDAC’s)

General Description

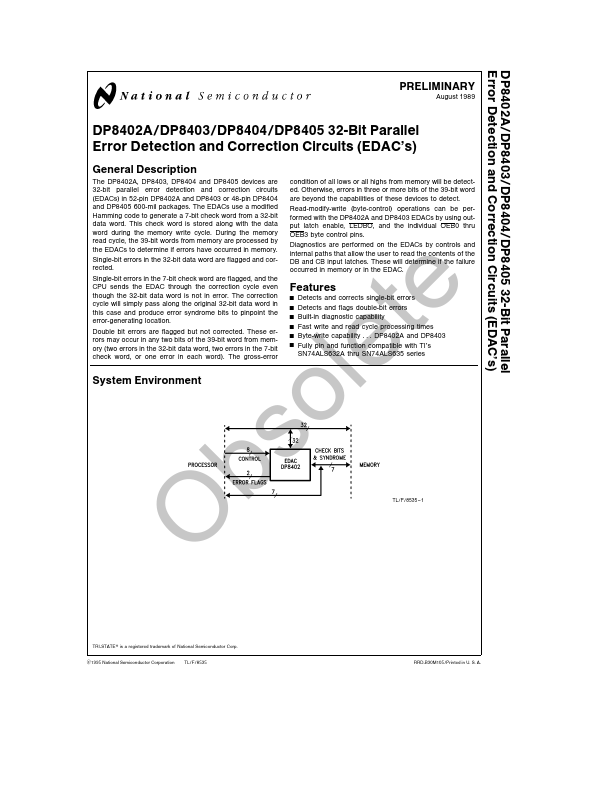

The DP8402A DP8403 DP8404 and DP8405 devices are 32-bit parallel error detection and correction circuits (EDACs) in 52-pin DP8402A and DP8403 or 48-pin DP8404 and DP8405 600-mil packages The EDACs use a modified Hamming code to generate a 7-bit check word from a 32-bit data word This check word is stored along with the data word during the memory write cycle During the memory read cycle the 39-bit words from memory are processed by the EDACs to...