DP8406

DP8406 is 32-Bit Parallel Error Detection and Correction Circuit manufactured by National Semiconductor.

DP8406 (54F 74F632) 32-Bit Parallel Error Detection and Correction Circuit

May 1991

DP8406 (54F 74F632) 32-Bit Parallel Error Detection and Correction Circuit

General Description

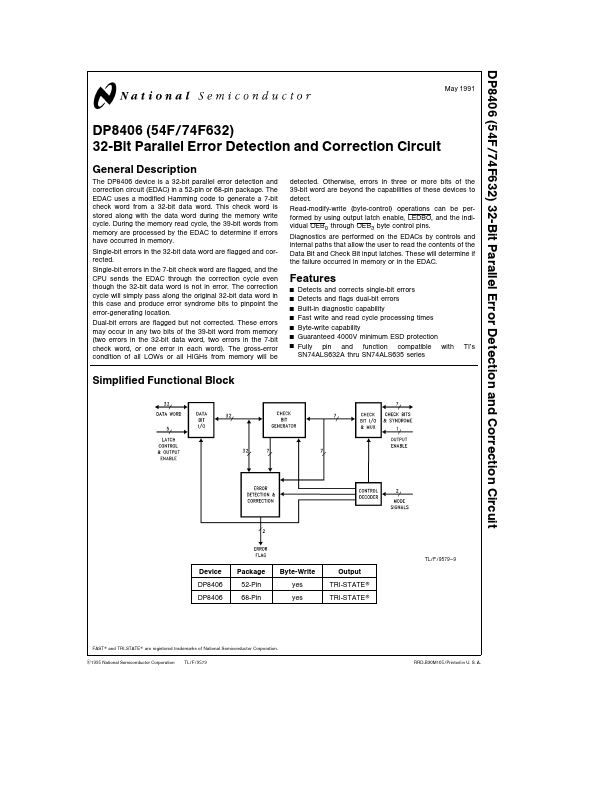

The DP8406 device is a 32-bit parallel error detection and correction circuit (EDAC) in a 52-pin or 68-pin package The EDAC uses a modified Hamming code to generate a 7-bit check word from a 32-bit data word This check word is stored along with the data word during the memory write cycle During the memory read cycle the 39-bit words from memory are processed by the EDAC to determine if errors have occurred in memory Single-bit errors in the 32-bit data word are flagged and corrected Single-bit errors in the...