DP8419 Overview

Key Specifications

Description

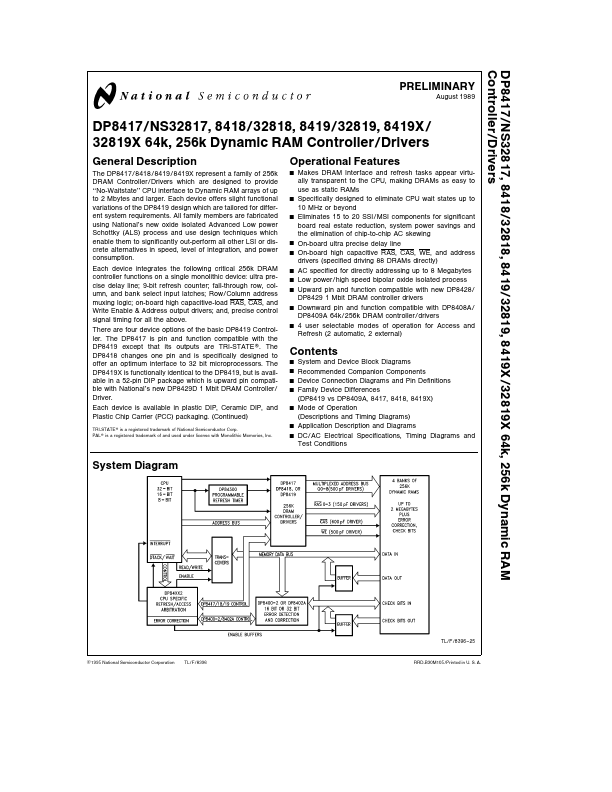

The DP8417 8418 8419 8419X represent a family of 256k DRAM Controller Drivers which are designed to provide ‘‘No-Waitstate’’ CPU interface to Dynamic RAM arrays of up to 2 Mbytes and larger Each device offers slight functional variations of the DP8419 design which are tailored for different system requirements All family members are fabricated using National’s new oxide isolated Advanced Low power Schottky (ALS) process and use design techniques which enable them to significantly out-perform all other LSI or discrete alternatives in speed level of integration and power consumption Each device integrates the following critical 256k DRAM controller functions on a single monolithic device ultra precise delay line 9-bit refresh counter fall-through row column and bank select input latches Row Column address muxing logic on-board high capacitive-load RAS CAS and Write Enable Address output drivers and precise control signal timing for all the above There are four device options of the basic DP8419 Controller The DP8417 is pin and function compatible with the DP8419 except that its outputs are TRI-STATE The DP8418 changes one pin and is specifically designed to offer an optimum interface to 32 bit microprocessors The DP8419X is functionally identical to the DP8419 but is available in a 52-pin DIP package which is upward pin compatible with National’s new DP8429D 1 Mbit DRAM Controller Driver Each device is available in plastic DIP Ceramic DIP and Plastic Chip Carrier (PCC) packaging (Continued) TRI-STATE is a registered trademark of National Semiconductor Corp PAL is a registered trademark of and used under license with Monolithic Memories Inc Operational Features Y Y Y Y Y Y Y Y Y Y Makes DRAM Interface and refresh tasks appear v.

Key Features

- Y Y Y Y Y Y Y Y Y Y Makes DRAM Interface and refresh tasks appear v