DP8473

DP8473 is Floppy Disk Controller PLUS-2 manufactured by National Semiconductor.

Description

This controller is a full featured floppy disk controller that is software patible with the m PD765A but also includes many additional hardware and software enhancements These enhancements include additional logic specifically required for an IBM PC PC-XT PC-AT or PS 2 design This controller incorporates a precision analog data separator that includes a self trimming delay line and VCO Up to three external filters are switched automatically depending on the data rate selected This provides optimal performance at the standard PC data rates of 250 300 kb s and 500 kb s It also enables optimum performance at 1 Mb s (MFM) These features bine to provide the lowest possible PLL bandwidth with the greatest lock range and hence the widest window margin This controller includes write prepensation circuitry A shift register is used to provide a fixed 125 ns early-late prepensation for all tracks at 500k 300k 250 kb s (83 ns for 1 MB s) or a prepensation value that scales with (Continued)

Features

Fully m PD765A and IBM-BIOS patible Integrates all PCXT PCAT and most PS 2 Logic On chip 24 MHz Crystal Oscillator DMA enable logic IBM patible address decode of A0

- A2 12 m A m P bus interface buffers 48 m A floppy drive interface buffers Data rate and drive control registers Precision analog data separator Self-calibrating PLL and delay line Automatically chooses one of three filters Intelligent read algorithm Two pin programmable prepensation modes Other enhancements up to 1 Mb s data rate Implied seek up to 4000 tracks IBM or ISO formatting Low power CMOS with power down mode

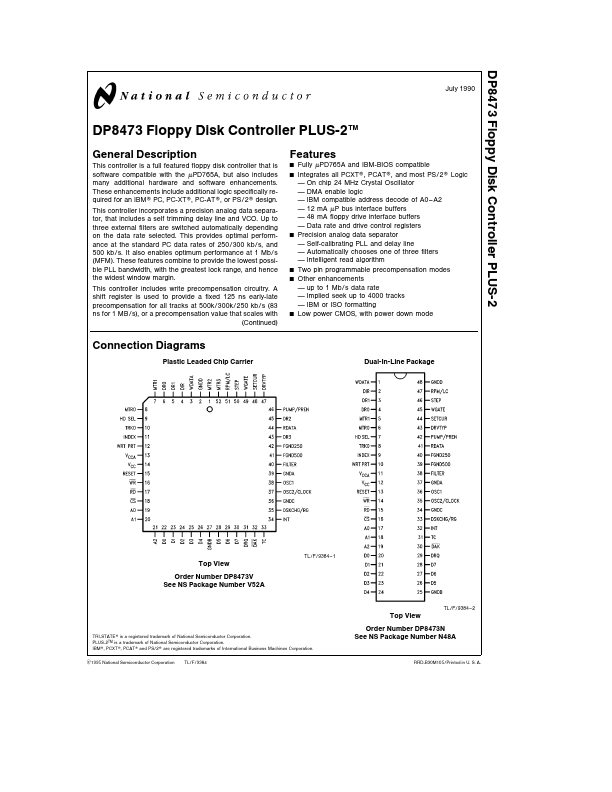

Connection Diagrams

Plastic Leaded Chip Carrier Dual-In-Line Package

TL F 9384

- 1

Top View Order Number DP8473V See NS Package Number V52A

TL F 9384

- 2

Top View

TRI-STATE is a registered trademark of National Semiconductor Corporation PLUS-2TM is a trademark of National Semiconductor Corporation IBM PCXT PCAT and PS 2 are registered trademarks of International Business...