DS32EL0124

DS32EL0124 is Deserializer manufactured by National Semiconductor.

DS32EL0124/DS32ELX0124 125

- 312.5 MHz Deserializer with DDR LVDS Parallel Interface

PRELIMINARY

May 9, 2008

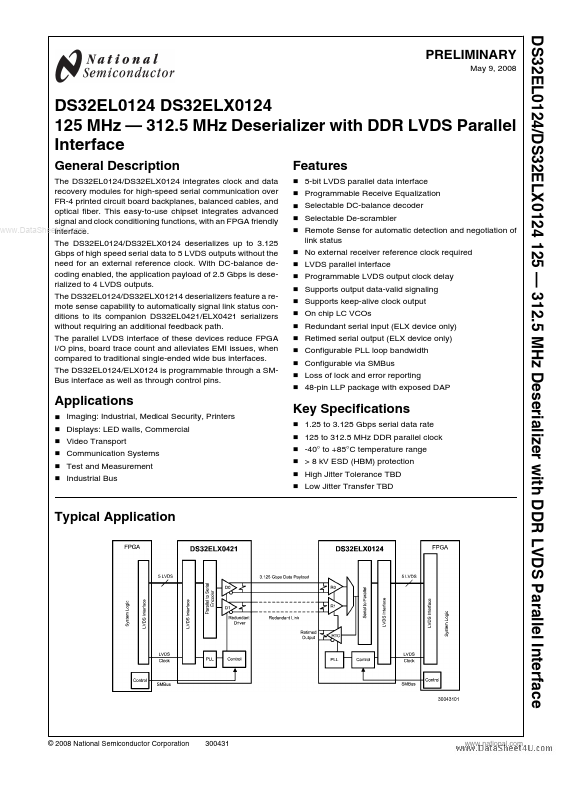

DS32EL0124 DS32ELX0124 125 MHz

- 312.5 MHz Deserializer with DDR LVDS Parallel Interface

General Description

The DS32EL0124/DS32ELX0124 integrates clock and data recovery modules for high-speed serial munication over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. This easy-to-use chipset integrates advanced signal and clock conditioning functions, with an FPGA friendly .. interface. The DS32EL0124/DS32ELX0124 deserializes up to 3.125 Gbps of high speed serial data to 5 LVDS outputs without the need for an external reference clock....