DS8837

Description

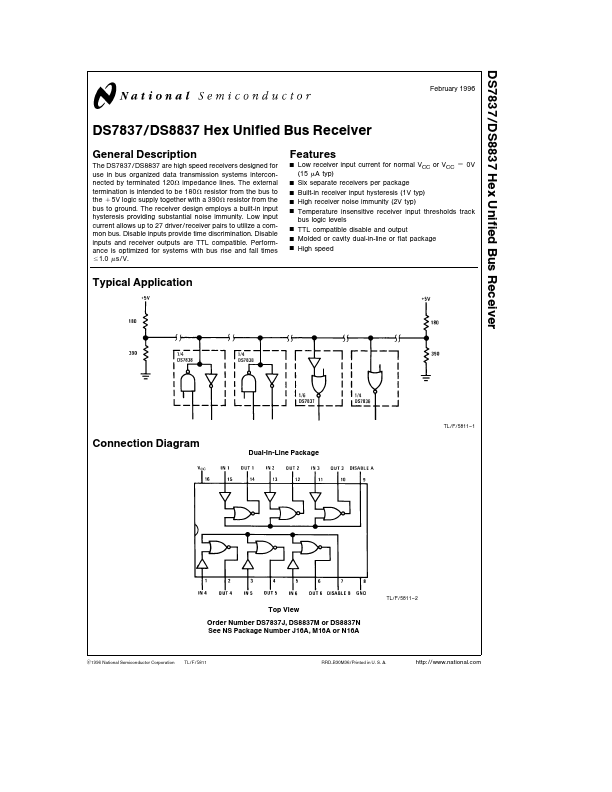

The DS7837 DS8837 are high speed receivers designed for use in bus organized data transmission systems interconnected by terminated 120X impedance lines The external termination is intended to be 180X resistor from the bus to the a 5V logic supply together with a 390X resistor from the bus to ground The receiver design employs a built-in input hysteresis providing substantial noise immunity Low input current allows up to 27 driver receiver pairs to utilize a mon bus Disable inputs provide time discrimination Disable inputs and receiver outputs are TTL patible Performance is optimized for systems with bus rise and fall times s 1 0 ms V.