DS90C365

DS90C365 is manufactured by National Semiconductor.

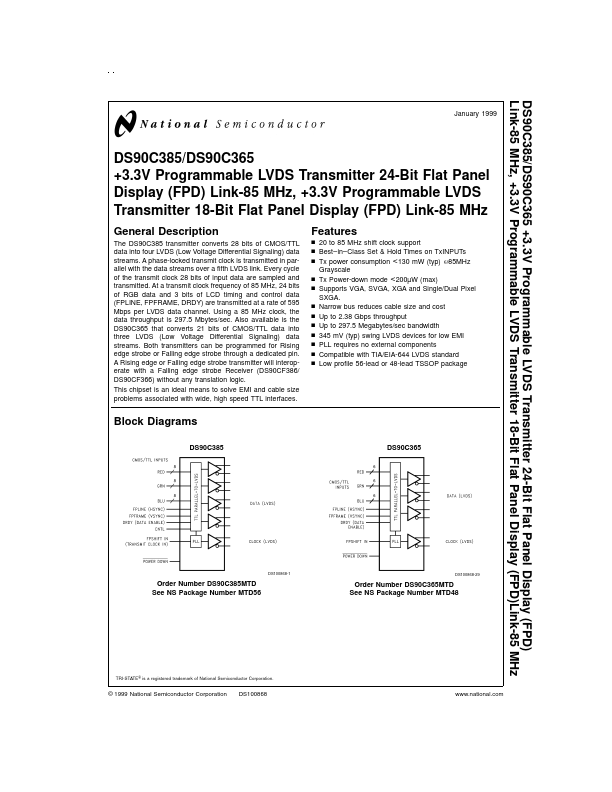

DS90C385/DS90C365 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link-85 MHz, +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD)Link-85 MHz

January 1999

DS90C385/DS90C365 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link-85 MHz, +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-85 MHz

General Description

The DS90C385 transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and...