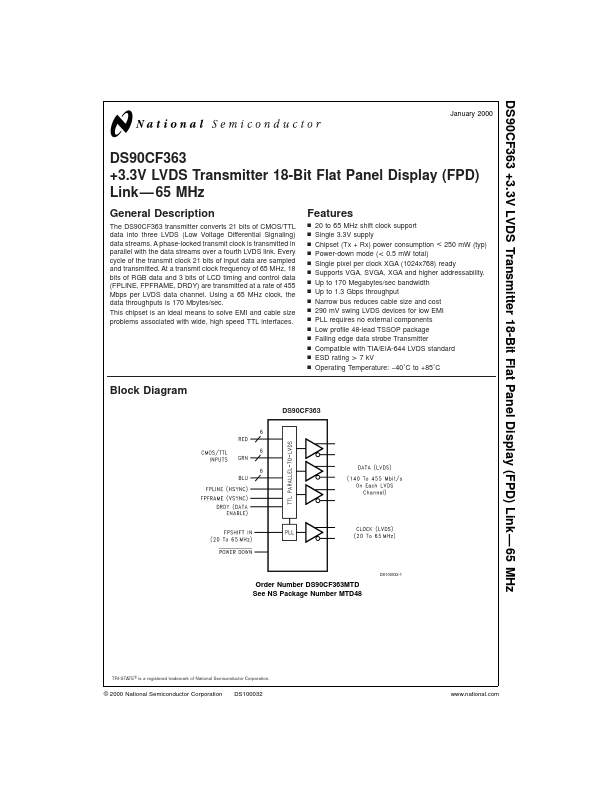

- Part: DS90CF363

- Description: +3.3V LVDS Transmitter

- Manufacturer: National Semiconductor

- Size: 184.76 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| DS90CF363B | Texas Instruments | +3.3V Programmable LVDS Transmitter |

| DS90CF366 | Texas Instruments | 3.3-V LVDS Receiver |

| DS90CF364 | Texas Instruments | +3.3V Programmable LVDS Transmitter |