DS90CF363B

Description

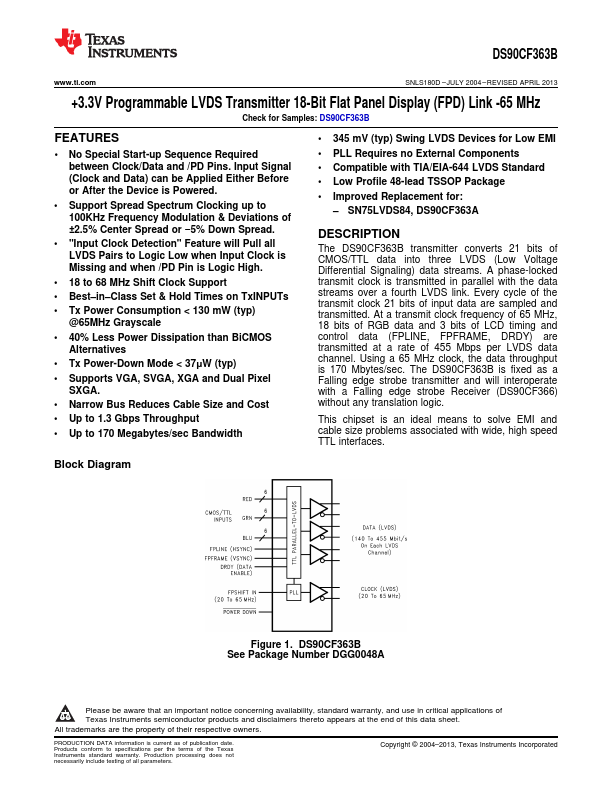

The DS90CF363B transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams.

Key Features

- Support Spread Spectrum Clocking up to 100KHz Frequency Modulation & Deviations of ±2.5% Center Spread or -5% Down Spread

- "Input Clock Detection" Feature will Pull all LVDS Pairs to Logic Low when Input Clock is Missing and when /PD Pin is Logic High

- 18 to 68 MHz Shift Clock Support

- Best-in-Class Set & Hold Times on TxINPUTs

- Tx Power Consumption < 130 mW (typ) @65MHz Grayscale

- 40% Less Power Dissipation than BiCMOS Alternatives

- Tx Power-Down Mode < 37μW (typ)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA

- Narrow Bus Reduces Cable Size and Cost

- Up to 1.3 Gbps Throughput