DS91M040

Description

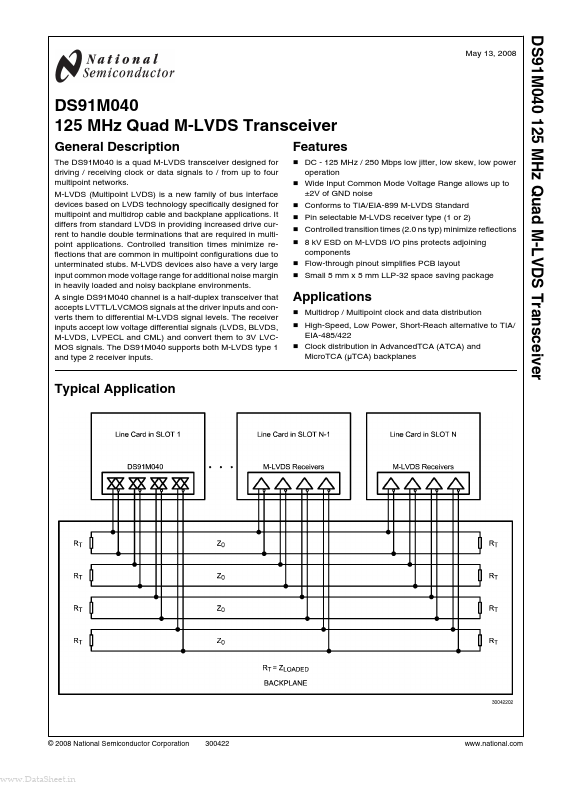

The DS91M040 is a quad M-LVDS transceiver designed for driving / receiving clock or data signals to / from up to four multipoint networks.

Key Features

- DC - 125 MHz / 250 Mbps low jitter, low skew, low power operation

- ±2V of GND noise Conforms to TIA/EIA-899 M-LVDS Standard Pin selectable M-LVDS receiver type (1 or

- Flow-through pinout simplifies PCB layout

- Small 5 mm x 5 mm LLP-32 space saving package