Datasheet Summary

FPD87392BXB +3.3V TFT-LCD Timing Controller with Dual LVDS Inputs/Dual RSDS™ Outputs for TFT-LCD Monitor and Notebook (SXGA/SXGA+/UXGA)

July 2004

FPD87392BXB +3.3V TFT-LCD Timing Controller with Dual LVDS Inputs/Dual RSDS™ Outputs for TFT-LCD Monitor and Notebook (SXGA/SXGA+/UXGA)

General Description

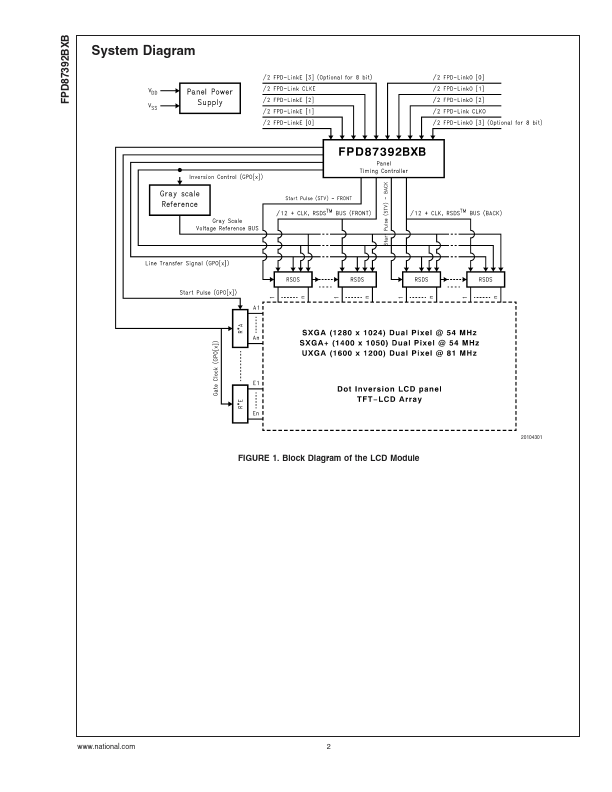

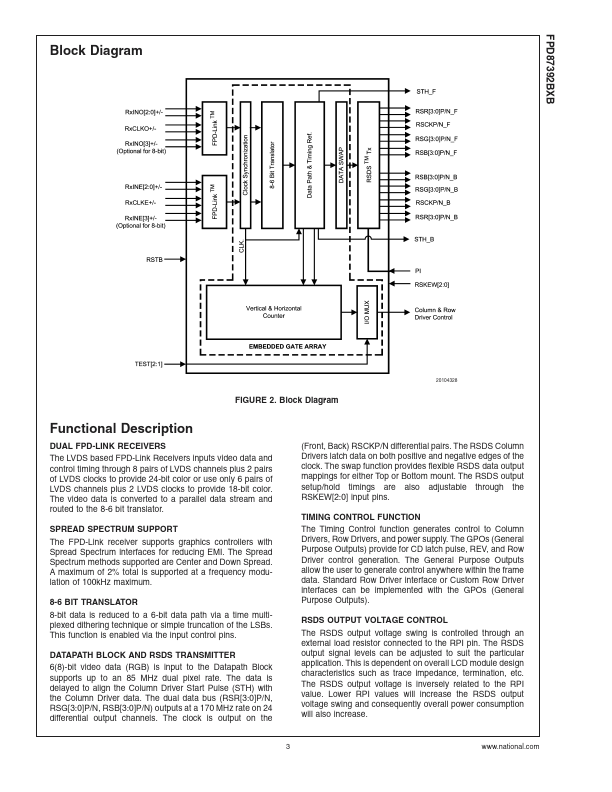

The FPD87392BXB Panel Timing Controller is an integrated FPD-Link + RSDS™ + TFT-LCD Timing Controller. The logic architecture is implemented using standard and default timing controller functionality based on an Embedded Gate Array. The device is reconfigurable to the needs of a specific application by providing user-defined specifications or customer supplied VHDL/Verilog code. The...