54AC169 Overview

Key Specifications

Operating Voltage: 5 V

Max Voltage (typical range): 6 V

Min Voltage (typical range): 2 V

Clock Edge Trigger: Positive Edge

Description

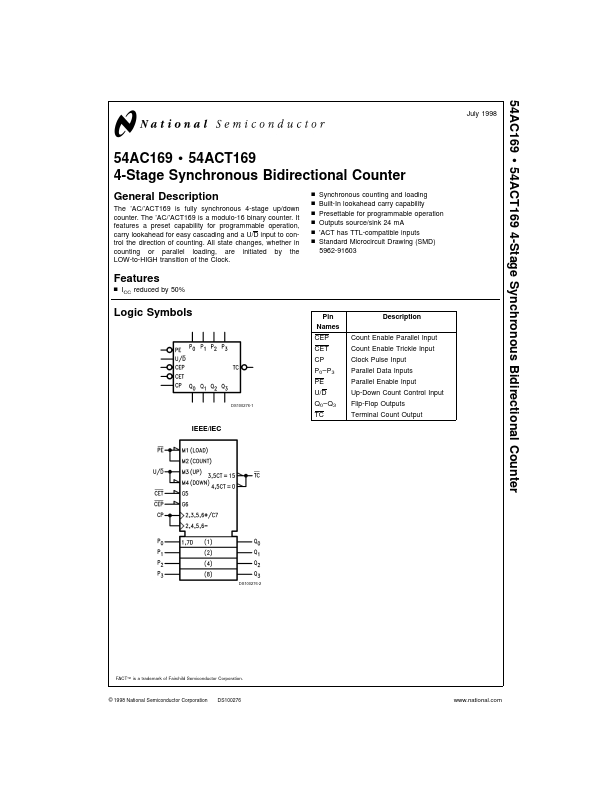

The ’AC/’ACT169 is fully synchronous 4-stage up/down counter. The ’AC/’ACT169 is a modulo-16 binary counter.

Key Features

- n ICC reduced by 50% Logic Symbols Pin Names CEP CET CP P0–P3 PE U/D DS100276-1