54ACTQ373

54ACTQ373 is Quiet Series Octal Transparent Latch manufactured by National Semiconductor.

- Part of the 54ACQ373 comparator family.

- Part of the 54ACQ373 comparator family.

Description

The ’ACQ/’ACTQ373 consists of eight latches with TRI-STATE outputs for bus organized system applications. The latches appear transparent to the data when Latch Enable (LE) is HIGH. When LE is low, the data satisfying the input timing requirements is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the bus output is in the high impedance state. The ’ACQ/’ACTQ373 utilizes NSC Quiet Series technology to guarantee quiet output switching and improve dynamic threshold performance. FACT Quiet Series™ features

GTO™ output control and undershoot corrector in addition to a split ground bus for superior performance.

Features n ICC and IOZ reduced by 50% n Guaranteed simultaneous switching noise level and dynamic threshold performance n Improved latch up immunity n Eight latches in a single package n TRI-STATE outputs drive bus lines or buffer memory address registers n Outputs source/sink 24 m A n Faster prop delays than the standard ’AC/’ACT373 n 4 k V minimum ESD immunity (’ACQ) n Standard Military Drawing (SMD)

- ’ACTQ373: 5962-92188

- ’ACQ373: 5962-92178

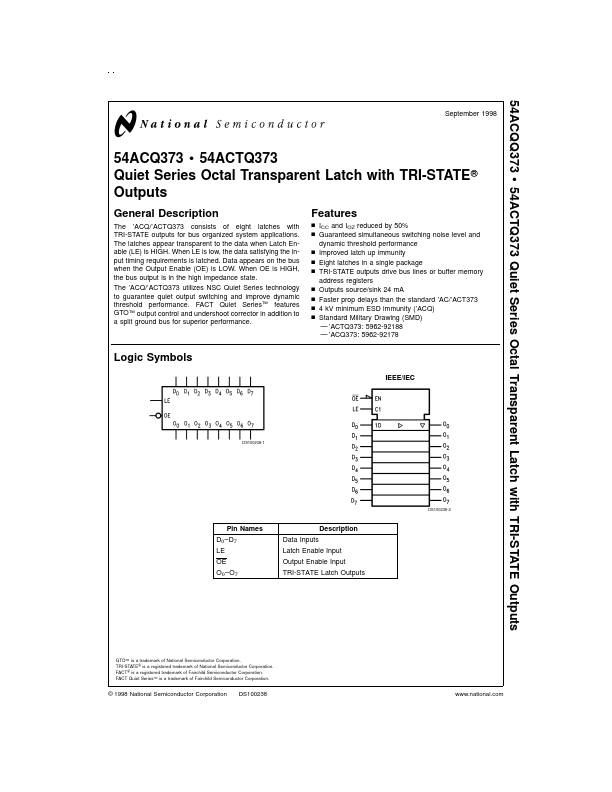

Logic Symbols

IEEE/IEC

DS100238-1

DS100238-2

Pin Names D0- D7 LE OE O0- O7 Data Inputs

Description

Latch Enable Input Output Enable Input TRI-STATE Latch Outputs

GTO™ is a trademark of National Semiconductor Corporation. TRI-STATE ® is a registered trademark of National Semiconductor Corporation. FACT ® is a registered trademark of Fairchild Semiconductor Corporation. FACT Quiet Series™ is a trademark of Fairchild Semiconductor Corporation.

© 1998 National Semiconductor Corporation

DS100238

.national.

Connection Diagrams

Pin Assignment for DIP and Flatpak Pin Assignment for LCC

DS100238-4

DS100238-3

Functional Description

The ’ACQ/’ACTQ373 contains eight D-type latches with TRI-STATE standard outputs. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change...