CGS748305

CGS748305 is Octal Divide-by-2 Skew Clock Driver manufactured by National Semiconductor.

Description

These minimum skew clock drivers are designed for high frequency Clock Generation & Support (CGS) applications. These devices are ideal for duty cycle recovery applications with internal frequency divide-by-2 circuitry. The devices guarantee minimum output skew across the outputs of a given device. Skew parameters are also provided as a means to measure duty cycle requirements as those found in high speed clocking systems.

Functional Description

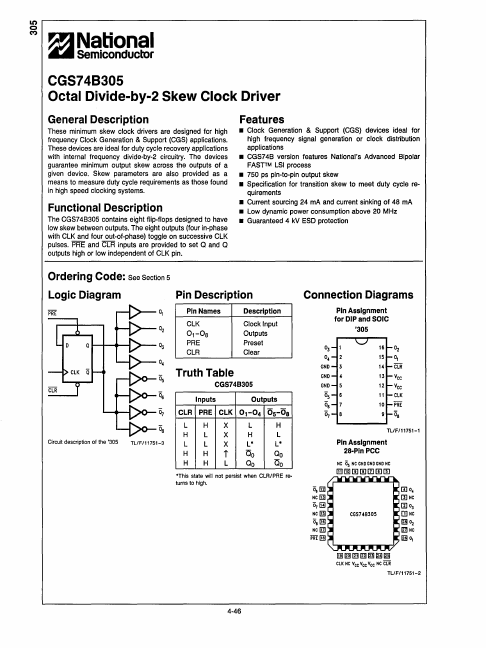

The CGS74B305 contains eight flip-flops designed to have low skew between outputs. The eight outputs (four in-phase with Cl K and four out-of-phase) toggle on successive Cl K a a pulses. PRE and Cl R inputs are provided to set and outputs high or low independent of Cl K pin.

Features

- Clock Generation & Support (CGS) devices ideal for high frequency signal generation or clock distribution applications

- CGS74B version features

National's Advanced Bipolar FASTTM l SI process

- 750 ps pin-to-pin output skew

- Specification for transition skew to meet duty cycle re- quirements

- Current sourcing 24 m A and current sinking of 48 m A

- low dynamic power consumption above 20 MHz

- Guaranteed 4 k V ESD protection

Ordering Code: See Section 5

Logic Diagram

Pin Description

Pin Names

Cl K 0 1-0 8 PRE Cl R

Description

Clock Input Outputs Preset Clear

Connection Diagrams

Pin Assignment for DIP and SOIC

'305

Circuit description of the '305

TLl F/I1751-3

Truth Table

CGS74B305

Inputs

Outputs

Cl R PRE Cl K 0 1-0 4 Os-Os l HX l

Hl

H l l l

X l- l-

H H i 00 00

HH l

"This state will not persist when CLR/PRE returns to...