CLC533

CLC533 is High-Speed 4:1 Analog Multiplexer manufactured by National Semiconductor.

- Part of the CLC comparator family.

- Part of the CLC comparator family.

Description

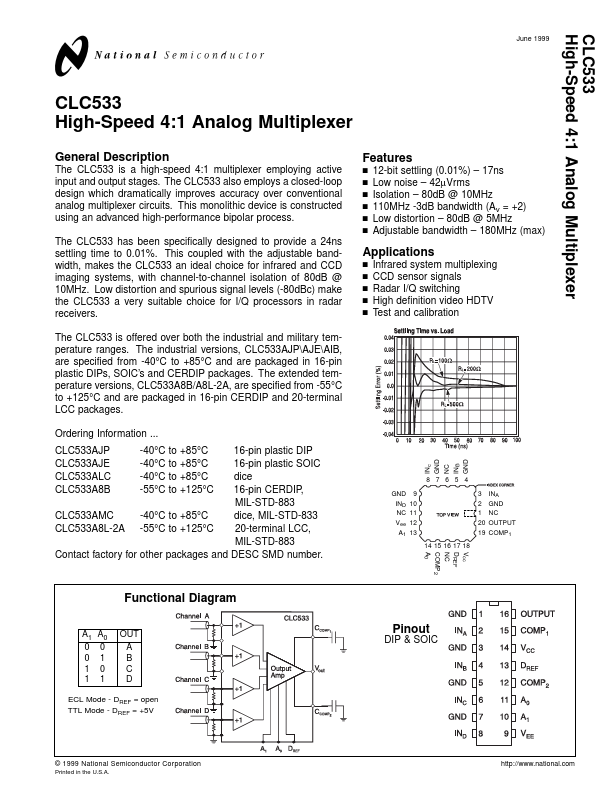

The CLC533 is a high-speed 4:1 multiplexer employing active input and output stages. The CLC533 also employs a closed-loop design which dramatically improves accuracy over conventional analog multiplexer circuits. This monolithic device is constructed using an advanced high-performance bipolar process. The CLC533 has been specifically designed to provide a 24ns settling time to 0.01%. This coupled with the adjustable bandwidth, makes the CLC533 an ideal choice for infrared and CCD imaging systems, with channel-to-channel isolation of 80d B @ 10MHz. Low distortion and spurious signal levels (-80d Bc) make the CLC533 a very suitable choice for I/Q processors in radar receivers. The CLC533 is offered over both the industrial and military temperature ranges. The industrial versions, CLC533AJPAJEAIB, are specified from -40°C to +85°C and are packaged in 16-pin plastic DIPs, SOIC’s and CERDIP packages. The extended temperature versions, CLC533A8B/A8L-2A, are specified from -55°C to +125°C and are packaged in 16-pin CERDIP and 20-terminal LCC packages. Ordering Information ... CLC533AJP CLC533AJE CLC533ALC CLC533A8B 16-pin plastic DIP 16-pin plastic SOIC dice 16-pin CERDIP, MIL-STD-883 CLC533AMC -40°C to +85°C dice, MIL-STD-833 CLC533A8L-2A -55°C to +125°C 20-terminal LCC, MIL-STD-883 Contact factory for other packages and DESC SMD number. -40°C -40°C -40°C -55°C to to to to +85°C +85°C +85°C +125°C

INc GND NC INB GND 8 7 6 5 4 GND IND NC Vee A1 9 10 11 12 13 14 15 16 17 18 Vcc DREF NC P2 A0 3 2 1 20 19 INA GND NC OUTPUT P1

Features s s s s s s

12-bit settling (0.01%)

- 17ns Low noise

- 42µVrms Isolation

- 80d B @ 10MHz 110MHz -3d B bandwidth (Av = +2) Low distortion

- 80d B @ 5MHz Adjustable bandwidth

- 180MHz (max) Infrared system multiplexing CCD sensor signals Radar I/Q switching High definition video HDTV Test and calibration

Applications s s s s s

Functional Diagram

A1 0 0 1 1 A0 0 1 0 1 OUT A B C D

Pinout

DIP & SOIC

ECL Mode

- DREF = open TTL Mode

-...