DM54L95

DM54L95 is 4-Bit Parallel Access Shift Registers manufactured by National Semiconductor.

Description

These 4-bit registers feature parallel and serial inputs parallel output mode control and two clock inputs The registers have three modes of operation Parallel (broadside) load Shift right (the direction QA toward QD) Shift left (the direction QD toward QA) Parallel loading is acplished by applying the four bits of data and taking the mode control input high The data is loaded into the associated flip-flops and appears at the outputs after the high-to-low transition of the clock-2 input During loading the entry of serial data is inhibited Shift right is acplished on the high-to-low transition of clock 1 when the mode control is low shift left is acplished on the high-to-low transition of clock 2 when the mode control is high by connecting the output of each flipflop to the parallel input of the previous flip-flop (QD to input C etc ) and serial data is entered at input D The clock input may be applied simultaneously to clock 1 and clock 2 if both modes can be clocked from the same source Changes at the mode control input should normally be made while both clock inputs are low however conditions described in the last three lines of the truth table will also ensure that register contents are protected

Features

Typical maximum clock frequency 14 MHz Typical power dissipation m W

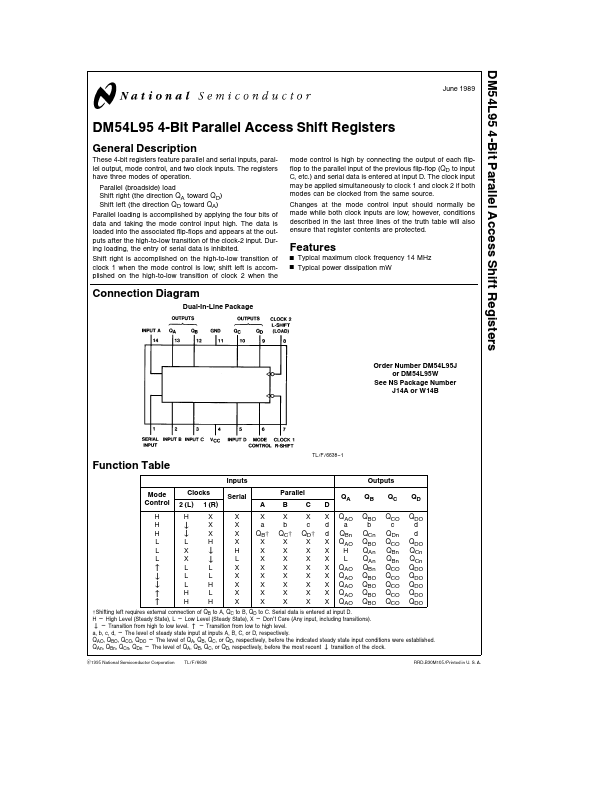

Connection Diagram

Dual-In-Line Package

Order Number DM54L95J or DM54L95W See NS Package Number J14A or W14B

TL F 6638

- 1

Function Table

Inputs Mode Control H H H L L L Clocks 2 (L) H 1 (R) X X X H X X X X H L X X X X X Serial A X a QB X X X X X X X X Parallel B X b QC X X X X X X X X C X c QD X X X X X X X X D X d d X X X X X X X X QAO a QBn QAO H L QAO QAO QAO QAO QAO QBO b QCn QBO QAn QAn QBn QBO QBO QBO QBO QCO c QDn QCO QBn QBn QCO QCO QCO QCO QCO QDO d d QDO QCn QCn QDO QDO QDO QDO QDO QA Outputs QB QC QD v v

L X X L L L H H u v v u u v v v

L L H L H

Shifting left requires external connection of QB to A QC to B QD to C Serial data is entered at input D H e High...