DM54LS373

DM54LS373 is Octal D-Type Transparent Latches and Edge-Triggered Flip-Flops manufactured by National Semiconductor.

Description

These 8-bit registers feature totem-pole TRI-STATE outputs designed specifically for driving highly-capacitive or relative- ly low-impedance loads The high-impedance state and in- creased high-logic level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for inter- face or pull-up ponents They are particularly attractive for implementing buffer registers I O ports bidirectional bus drivers and working registers

(Continued)

Features

Y Choice of 8 latches or 8 D-type flip-flops in a single package

Y TRI-STATE bus-driving outputs Y Full parallel-access for loading Y Buffered control inputs Y P-N-P inputs reduce D-C loading on data lines

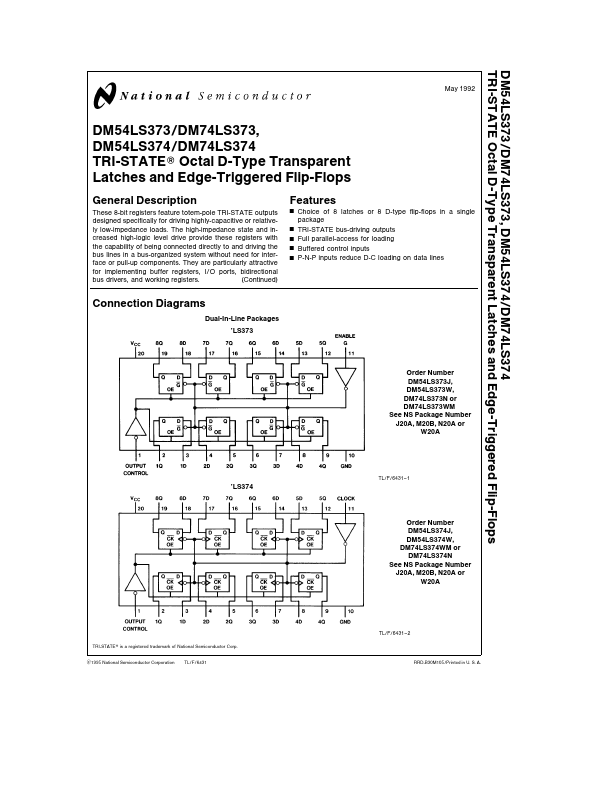

Connection Diagrams

Dual-In-Line Packages ’LS373

Order Number DM54LS373J DM54LS373W DM74LS373N or DM74LS373WM See NS Package Number J20A M20B N20A or

W20A

’LS374

TL F 6431

- 1

Order Number DM54LS374J DM54LS374W DM74LS374WM or DM74LS374N See NS Package Number J20A M20B N20A or

W20A

TRI-STATE is a registered trademark of National Semiconductor Corp C1995 National Semiconductor Corporation TL F 6431

TL F 6431

- 2 RRD-B30M105 Printed in U S A

General Description

(Continued)

The eight latches of the DM54 74LS373 are transparent Dtype latches meaning that while the enable (G) is high the Q outputs will follow the data (D) inputs When the enable is taken low the output will be latched at the level of the data that was set up

The eight flip-flops of the DM54 74LS374 are edge-triggered D-type flip flops On the positive transition of the clock the Q outputs will be set to the logic states that were set up at the D inputs

A buffered output control input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state In the high-impedance state the outputs neither load nor drive the bus lines significantly

The output control does not affect the internal operation...