DP83220

DP83220 is CDL Twisted Pair FDDI Transceiver Device manufactured by National Semiconductor.

Description

The Copper Data Link (CDL) Transceiver is an integrated circuit designed to interface directly with the National Semiconductor FDDI Chip Set or other FDDI PHY silicon allowing low cost FDDI patible data links over copper based media The DP83220 Transceiver with the proper pensation selected will allow links of up to 100 meters over both Shielded Twisted Pair (STP) and Datagrade unshielded Twisted Pair (DTP) CDL surpasses a Bit Error Rate (BER) of k1 c 10b12 over both STP and DTP The CDL is designed to meet the SDDI specification for FDDI transmission across Type 1 STP cable when used in conjunction with the appropriate transformer filter module from Pulse Engineering

Features

Fully patible with current FDDI PHY standard Fully patible with the SDDI PMD specification Requires a single a 5V supply Isolated TX and RX power supplies for minimum noise coupling Allows use of Type 1 STP and Category 5 DTP cables No Transmit Clock required Loopback feature for board diagnostics Link Detect input provided

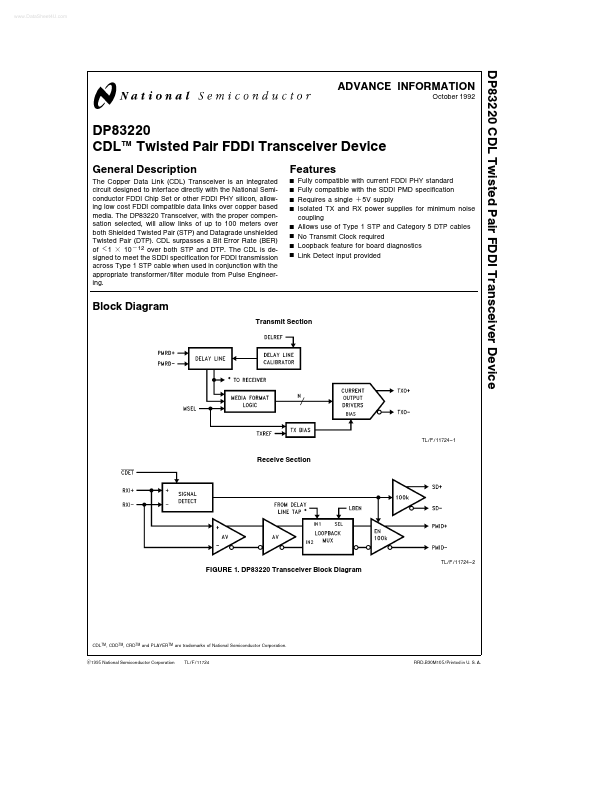

Block Diagram

Transmit Section

TL F 11724

- 1

Receive Section

TL F 11724

- 2

FIGURE 1 DP83220 Transceiver Block Diagram

CDLTM CDDTM CRDTM and PLAYERTM are trademarks of National Semiconductor Corporation

C1995 National Semiconductor Corporation

TL F 11724

RRD-B30M105 Printed in U S A

1 0 Functional Description

The CDL Transceiver consists of nine major functional blocks as shown in Figure 1 The Transmit section includes the following the Delay Line the Delay Line Calibrator the Media Format Logic and the Current Output Driver circuitry with its bias circuitry The Delay Line accepts the NRZI encoded data from the PMRD g pins and provides a short ‘‘memory’’ of the bit that preceded the bit currently being transmitted The Delay Line Calibrator allows the use of an external resistor which governs the time calibration of the delay line The Delay Line outputs the data via taps which are tied to the Media Format Logic The encoding logic is...