DP83261

DP83261 is BMAC Device manufactured by National Semiconductor.

Description

The DP83261 BMAC device implements the Media Access Control (MAC) protocol for operation in an FDDI token ring The BMAC device provides a flexible interface to the BSI-2TM device The BMAC device offers the capabilities described in the ANSI X3T9 5 MAC Standard and several functional enhancements allowed by the Standard The BMAC device transmits receives repeats and strips tokens and frames It uses a full duplex architecture that allows diagnostic transmission and self testing for error isolation The duplex architecture also allows full duplex data service on point-to-point connections Management software is also aided by an array of on chip statistical counters and the ability to internally generate Claim and Beacon frames without program intervention A multi-frame streaming interface is provided to the system interface device

Features

Full duplex operation with through parity Supports all FDDI ring scheduling classes (asynchronous synchronous restricted asynchronous and immediate) Supports individual group short long and external addressing Generates Beacon Claim and Void frames without intervention Provides extensive ring and station statistics Provides extensions for MAC level bridging Provides separate management interface Uses low power micro CMOS

TL F 10387

- 1

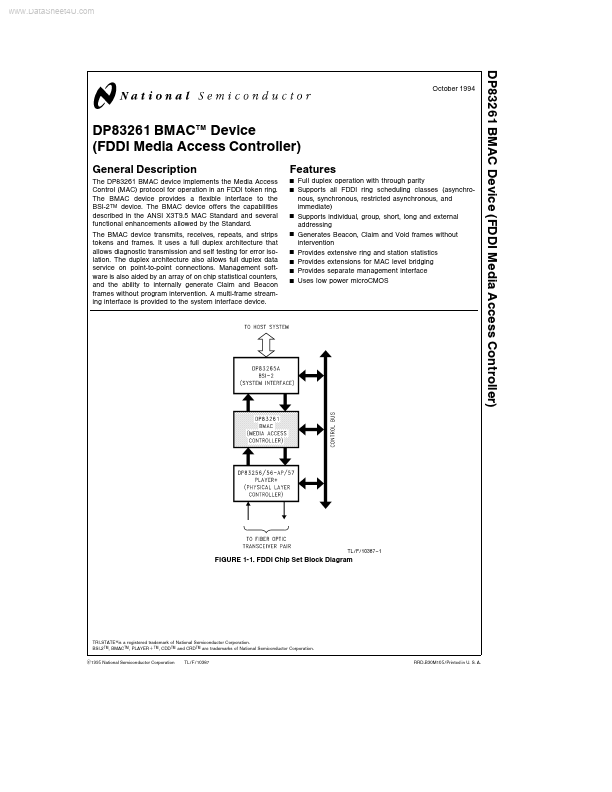

FIGURE 1-1 FDDI Chip Set Block Diagram

TRI-STATE is a registered trademark of National Semiconductor Corporation BSI-2TM BMACTM PLAYER a TM CDDTM and CRDTM are trademarks of National Semiconductor Corporation C1995 National Semiconductor Corporation TL F 10387 RRD-B30M105 Printed in U S A

Table of Contents

1 0 FDDI CHIP SET OVERVIEW

2 0 ARCHITECTURAL DESCRIPTION

2 1 Ring Engine 2 2 Interfaces 3 0 FEATURE

OVERVIEW

4 0 FDDI MAC FACILITIES 4 1 Symbol Set 4 2 Protocol Data Units 4 3 Frame Counts 4 4 Timers 4 5 Ring Scheduling 5 0 FUNCTIONAL DESCRIPTION

5 1 Token Handling 5 2 Servicing Transmission Requests 5 3 Request Service Parameters 5 4 Frame Validity Processing 5 5...