DS90CR288

DS90CR288 is +3.3V Rising Edge Data Strobe LVDS manufactured by National Semiconductor.

Description

The DS90CR287 (see DS90CR287/288A datasheet) transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phaselocked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. The DS90CR288 receiver converts the four LVDS data streams back into 28 bits of CMOS/TTL data. At a transmit clock frequency of 75 MHz, 28 bits of TTL data are transmitted at a rate of 525 Mbps per LVDS data channel. Using a 75 MHz clock, the data throughput is 2.10 Gbit/s (262.5 Mbytes/sec). plete specifications for the DS90CR287 are located in the DS90CR287/DS90CR288A datasheet. The DS90CR287 supports clock rates from 20 to 85 MHz. This chipset is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces.

Features n 20 to 75 MHz shift clock support n 50% duty cycle on receiver output clock n Best-in-Class Set & Hold Times on Tx INPUTs and Rx OUTPUTs n Low power consumption n Tx + Rx Powerdown mode < 400µW (max) n ± 1V mon-mode range (around +1.2V) n Narrow bus reduces cable size and cost n Up to 2.10 Gbps throughput n Up to 262.5 Mbytes/sec bandwidth n 345 m V (typ) swing LVDS devices for low EMI n PLL requires no external ponents n Rising edge data strobe n patible with TIA/EIA-644 LVDS standard n Low profile 56-lead TSSOP package

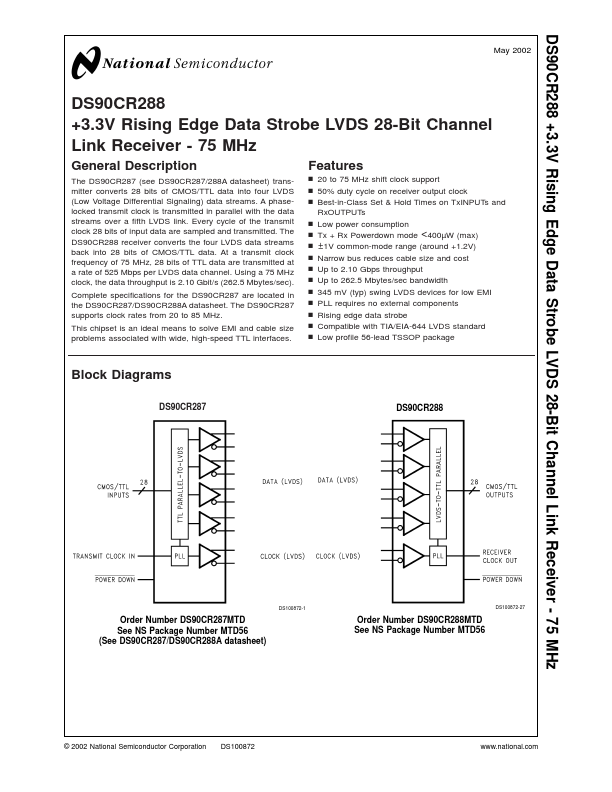

Block Diagrams

DS90CR287 DS90CR288

DS100872-1

DS100872-27

Order Number DS90CR287MTD See NS Package Number MTD56 (See DS90CR287/DS90CR288A datasheet)

Order Number DS90CR288MTD See NS Package Number MTD56

© 2002 National Semiconductor Corporation

DS100872

.national.

Pin Diagram

DS100872-22

Typical Application

DS100872-23

.national.

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for...