DS90CR288A

Overview

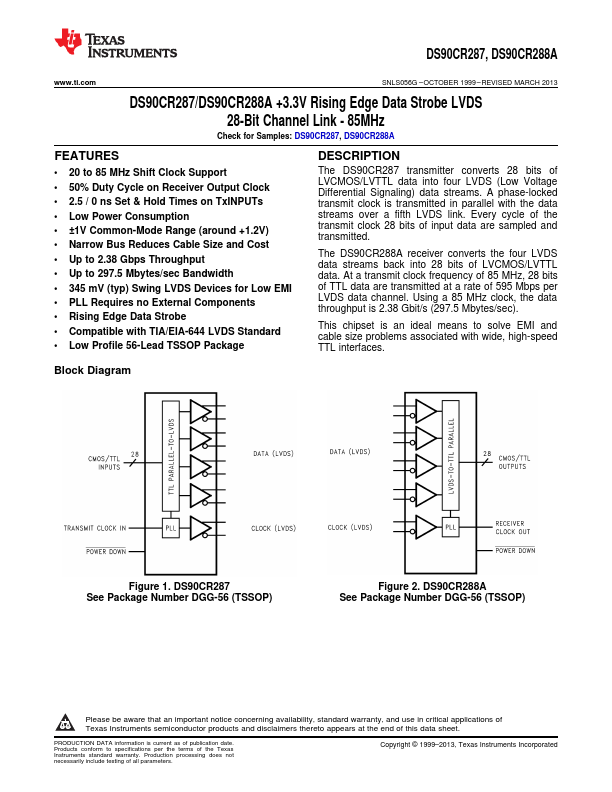

The DS90CR287 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link.

- 20 to 85 MHz Shift Clock Support

- 50% Duty Cycle on Receiver Output Clock

- 2.5 / 0 ns Set & Hold Times on TxINPUTs

- Low Power Consumption

- ±1V Common-Mode Range (around +1.2V)

- Narrow Bus Reduces Cable Size and Cost

- Up to 2.38 Gbps Throughput

- Up to 297.5 Mbytes/sec Bandwidth

- 345 mV (typ) Swing LVDS Devices for Low EMI

- PLL Requires no External Components