SCANSTA101

SCANSTA101 is Low Voltage IEEE 1149.1 STA Master manufactured by National Semiconductor.

Description

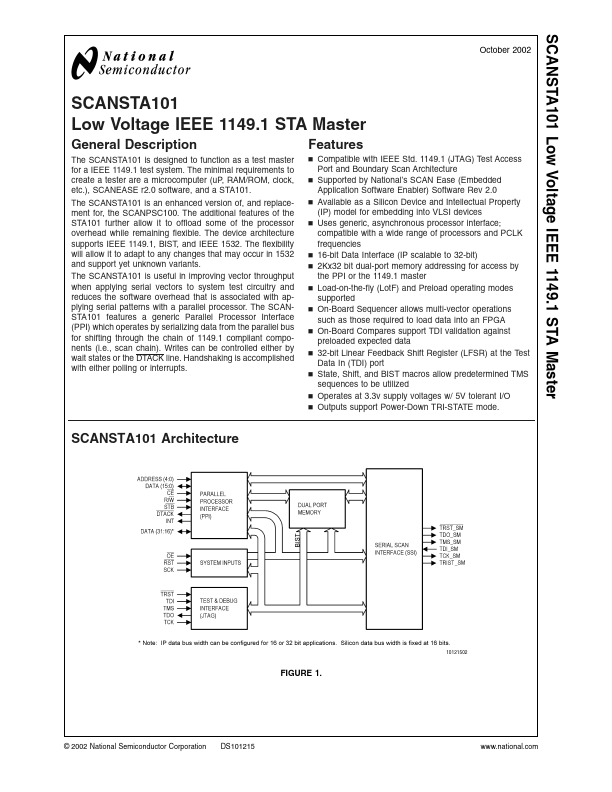

The SCANSTA101 is designed to function as a test master for a IEEE 1149.1 test system. The minimal requirements to create a tester are a microputer (u P, RAM/ROM, clock, etc.), SCANEASE r2.0 software, and a STA101. The SCANSTA101 is an enhanced version of, and replacement for, the SCANPSC100. The additional features of the STA101 further allow it to offload some of the processor overhead while remaining flexible. The device architecture supports IEEE 1149.1, BIST, and IEEE 1532. The flexibility will allow it to adapt to any changes that may occur in 1532 and support yet unknown variants. The SCANSTA101 is useful in improving vector throughput when applying serial vectors to system test circuitry and reduces the software overhead that is associated with applying serial patterns with a parallel processor. The SCANSTA101 features a generic Parallel Processor Interface (PPI) which operates by serializing data from the parallel bus for shifting through the chain of 1149.1 pliant ponents (i.e., scan chain). Writes can be controlled either by wait states or the DTACK line. Handshaking is acplished with either polling or interrupts.

Features n patible with IEEE Std. 1149.1 (JTAG) Test Access Port and Boundary Scan Architecture n Supported by National’s SCAN Ease (Embedded Application Software Enabler) Software Rev 2.0 n Available as a Silicon Device and Intellectual Property (IP) model for embedding into VLSI devices n Uses generic, asynchronous processor interface; patible with a wide range of processors and PCLK frequencies n 16-bit Data Interface (IP scalable to 32-bit) n 2Kx32 bit dual-port memory addressing for access by the PPI or the 1149.1 master n Load-on-the-fly (Lot F) and Preload operating modes supported n On-Board Sequencer allows multi-vector operations such as those required to load data into an FPGA n On-Board pares support TDI validation against preloaded expected data n 32-bit Linear Feedback Shift Register (LFSR) at the Test Data In (TDI)...