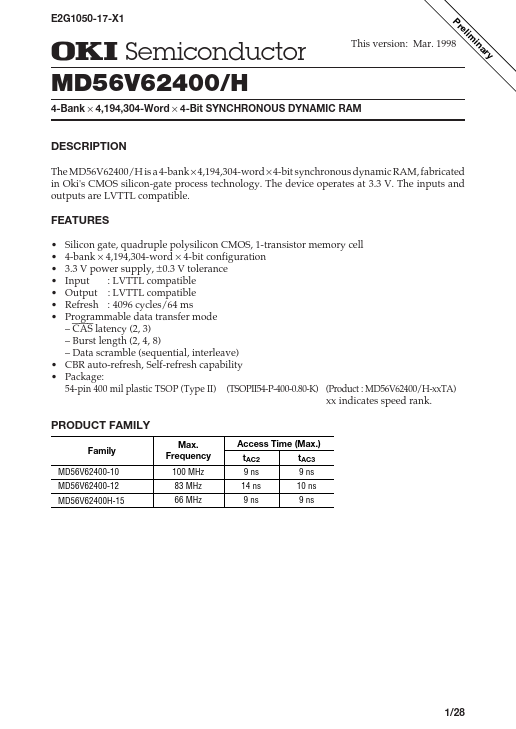

MD56V62400

Overview

The MD56V62400/H is a 4-bank ¥ 4,194,304-word ¥ 4-bit synchronous dynamic RAM, fabricated in Oki's CMOS silicon-gate process technology. The device operates at 3.3 V.

- Silicon gate, quadruple polysilicon CMOS, 1-transistor memory cell 4-bank ¥ 4,194,304-word ¥ 4-bit configuration 3.3 V power supply, ± 0.3 V tolerance Input : LVTTL compatible Output : LVTTL compatible Refresh : 4096 cycles/64 ms Programmable data transfer mode - CAS latency (2, 3) - Burst length (2, 4, 8) - Data scramble (sequential, interleave)

- CBR auto-refresh, Self-refresh capability

- Package: 54-pin 400 mil plastic TSOP (Type II) (TSOPII54-P-400-0.80-K) (Product : MD56V62400/H-xxTA) xx indicates speed rank.