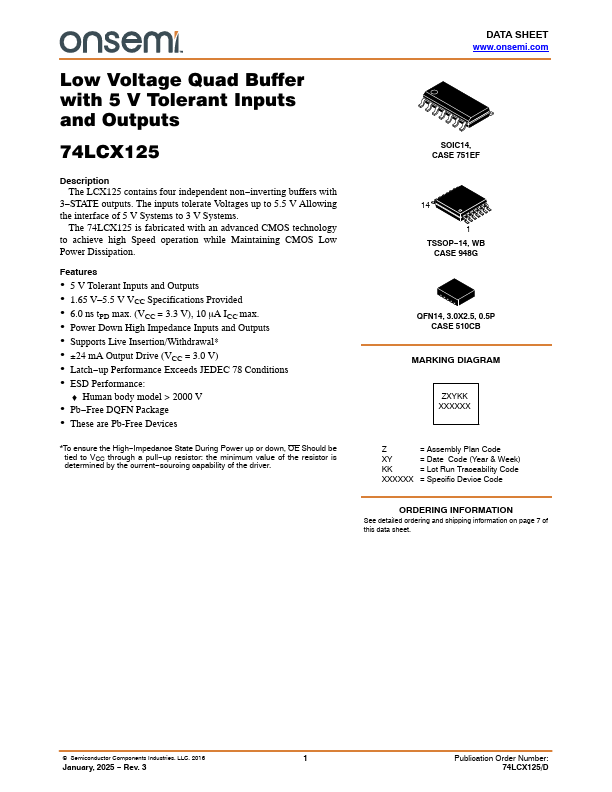

74LCX125

Overview

An OEn On DAP Inputs Output Enable Inputs Outputs No Connect NOTE: Die Attach Pad (DIE) TRUTH.

- 5 V Tolerant Inputs and Outputs

- 1.65 V-5.5 V VCC Specifications Provided

- 6.0 ns tPD max. (VCC = 3.3 V), 10 mA ICC max.

- Power Down High Impedance Inputs and Outputs

- Supports Live Insertion/Withdrawal*

- 24 mA Output Drive (VCC = 3.0 V)

- Latch-up Performance Exceeds JEDEC 78 Conditions

- ESD Performance: Human body model > 2000 V

- Pb-Free DQFN Package

- These are Pb-Free Devices