CAT24C05 Overview

Description

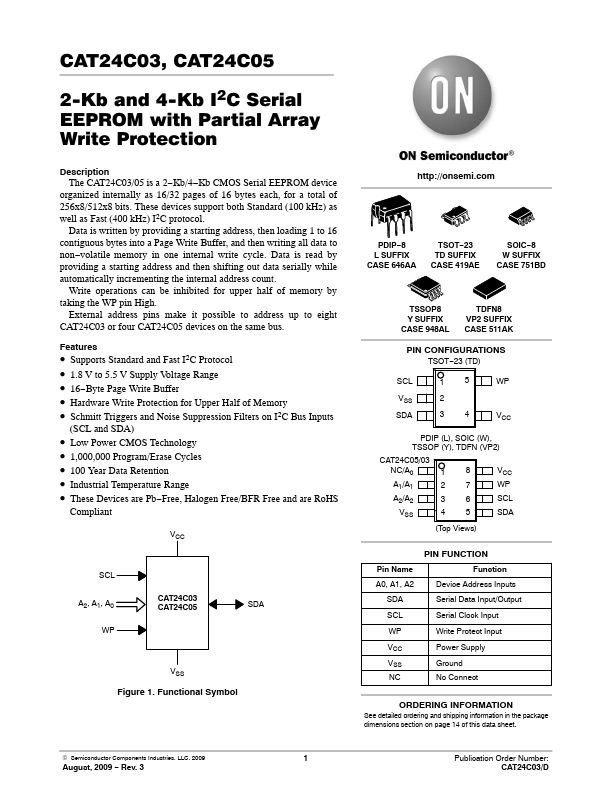

The CAT24C03/05 is a 2-Kb/4-Kb CMOS Serial EEPROM device organized internally as 16/32 pages of 16 bytes each, for a total of 256x8/512x8 bits. These devices support both Standard (100 kHz) as well as Fast (400 kHz) I2C protocol.

Key Features

- Supports Standard and Fast I2C Protocol

- 1.8 V to 5.5 V Supply Voltage Range

- 16-Byte Page Write Buffer

- Hardware Write Protection for Upper Half of Memory

- Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs (SCL and SDA)

- Low Power CMOS Technology

- 1,000,000 Program/Erase Cycles

- 100 Year Data Retention

- Industrial Temperature Range

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant VCC SCL A2, A1, A0 WP CAT24C03 CAT24C05 SDA VSS Figure