MC100E193

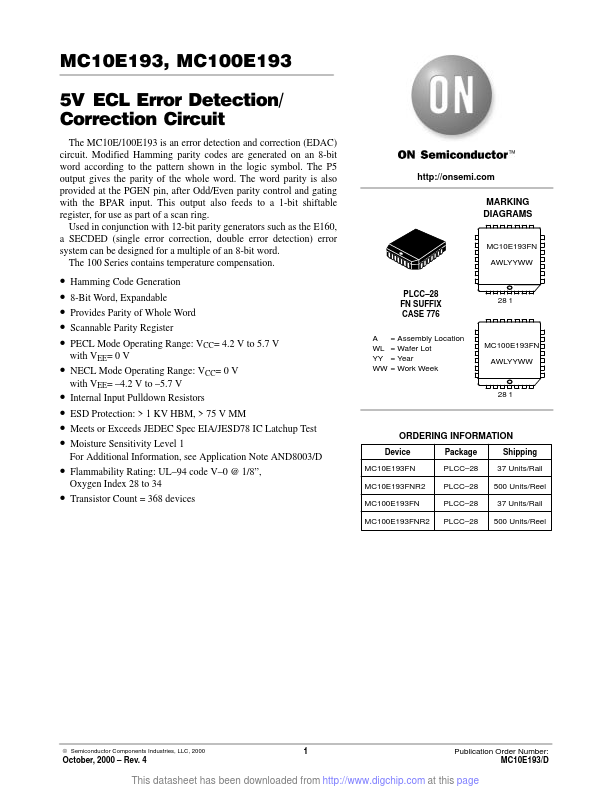

MC10E193, MC100E193

5VĄECL Error Detection/ Correction Circuit

The MC10E/100E193 is an error detection and correction (EDAC) circuit. Modified Hamming parity codes are generated on an 8-bit word according to the pattern shown in the logic symbol. The P5 output gives the parity of the whole word. The word parity is also provided at the PGEN pin, after Odd/Even parity control and gating with the BPAR input. This output also feeds to a 1-bit shiftable register, for use as part of a scan ring.

Used in conjunction with 12-bit parity generators such as the E160, a SECDED (single error correction, double error detection) error system can be designed for a multiple of an 8-bit word.

The 100 Series contains temperature pensation.

- Hamming Code Generation

- 8-Bit Word, Expandable

- Provides Parity of Whole Word

- Scannable Parity Register

- PECL Mode Operating Range: VCC= 4.2 V to 5.7 V with VEE= 0 V

- NECL Mode Operating Range: VCC= 0 V with VEE=

- 4.2 V to

- 5.7 V

-...