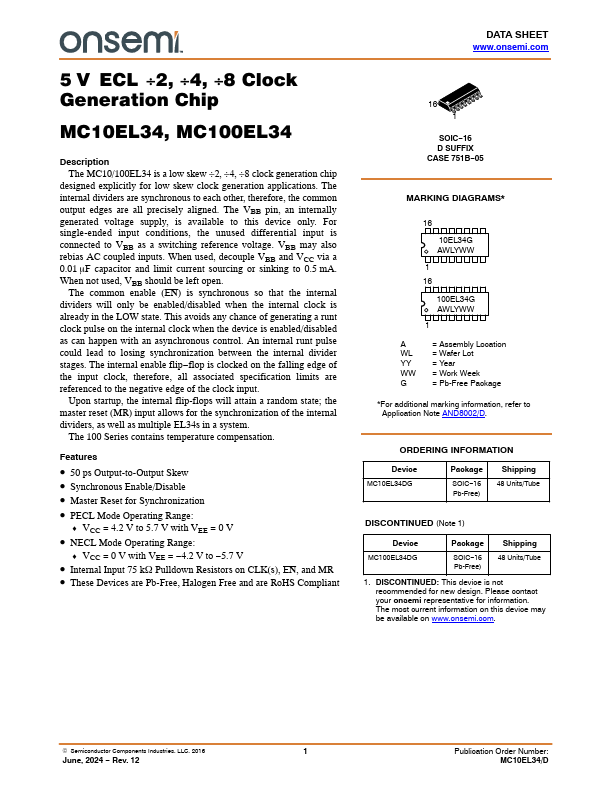

MC100EL34

Overview

- 50 ps Output-to-Output Skew

- Synchronous Enable/Disable

- Master Reset for Synchronization

- PECL Mode Operating Range:

- VCC = 4.2 V to 5.7 V with VEE = 0 V

- NECL Mode Operating Range:

- VCC = 0 V with VEE = -4.2 V to -5.7 V

- Internal Input 75 kW Pulldown Resistors on CLK(s), EN, and MR

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant