MC100EP131 Overview

Key Specifications

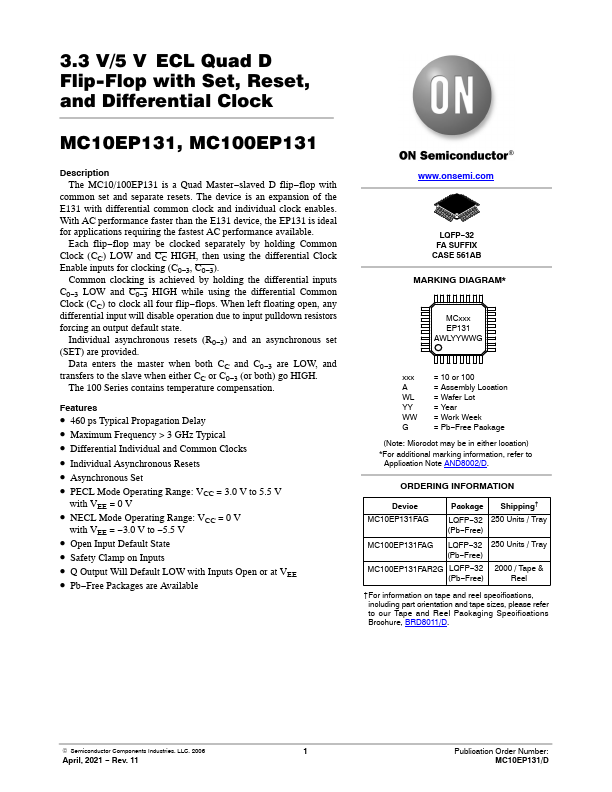

Package: LQFP

Mount Type: Surface Mount

Pins: 32

Operating Voltage: 3.3 V

Description

The MC10/100EP131 is a Quad Master-slaved D flip-flop with common set and separate resets. The device is an expansion of the E131 with differential common clock and individual clock enables.

Key Features

- 460 ps Typical Propagation Delay

- Maximum Frequency > 3 GHz Typical

- Differential Individual and Common Clocks

- Individual Asynchronous Resets

- Asynchronous Set