MC100EP809 Description

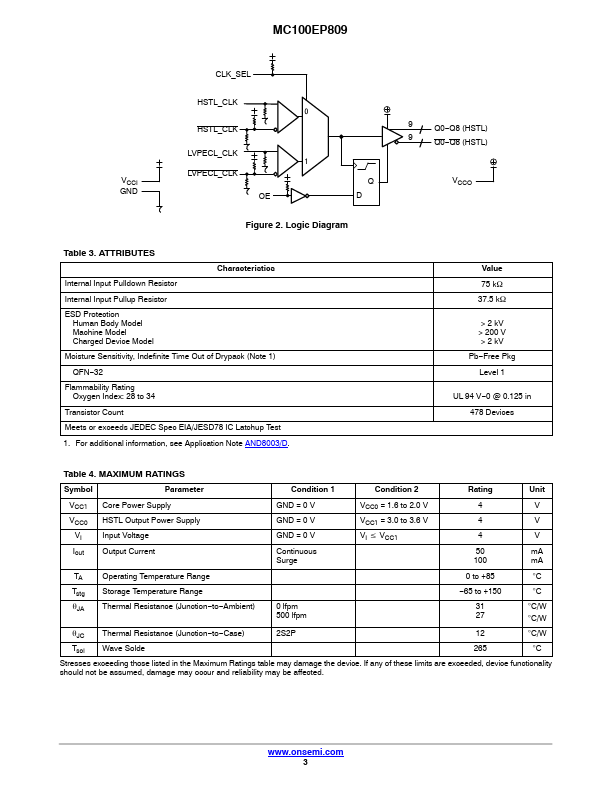

The MC100EP809 is a low skew 2:1:9 differential clock driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The part is designed for use in low voltage applications which require a large number of outputs to drive precisely aligned low skew signals to their destination. The two clock inputs are one differential HSTL and one differential LVPECL.

MC100EP809 Key Features

- 100 ps Typical Device-to-Device Skew

- 15 ps Typical within Device Skew

- HSTL patible Outputs Drive 50 W to GND with no

- Maximum Frequency > 750 MHz

- 850 ps Typical Propagation Delay

- Fully patible with Micrel SY89809L

- PECL and HSTL Mode Operating Range: VCCI = 3 V to 3.6 V

- Open Input Default State

- This Device is Pb-Free and is RoHS pliant

- For additional marking information, refer to Application Note AND8002/D

MC100EP809 Applications

- 100 ps Typical Device−to−Device Skew