MC100EP91 Description

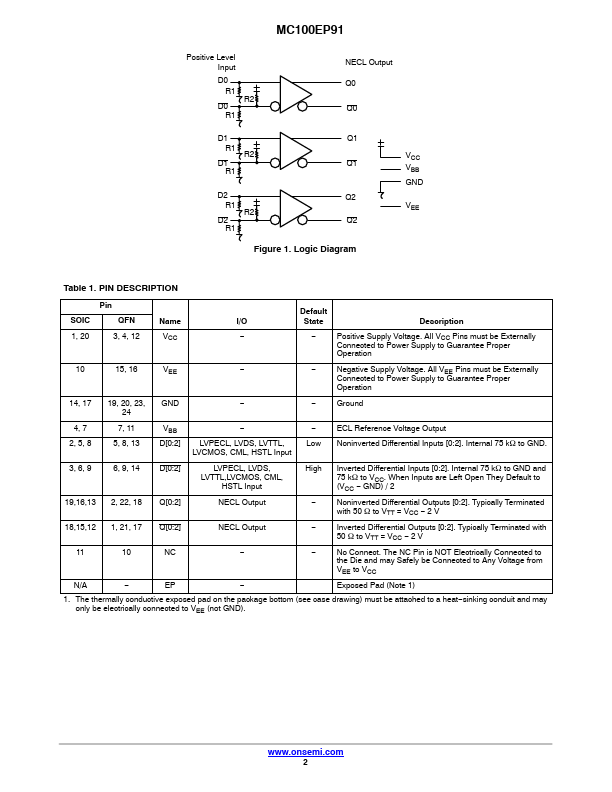

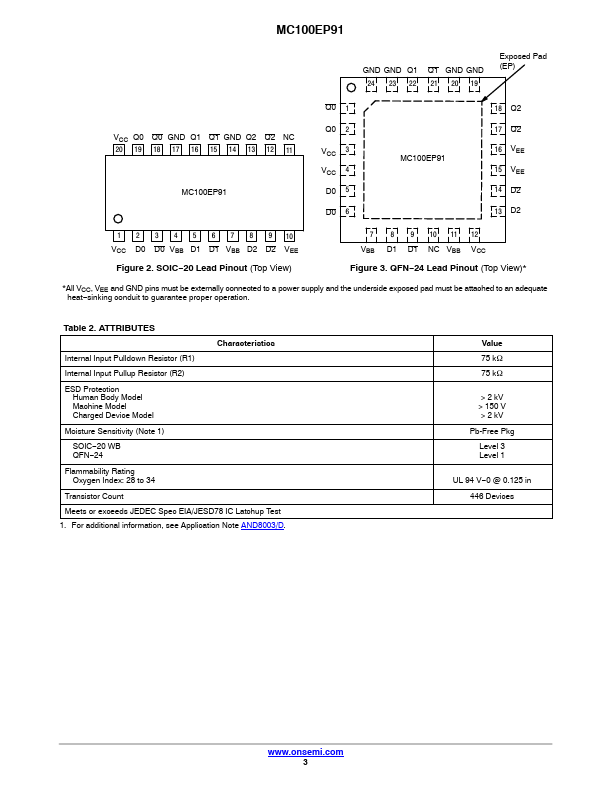

The MC100EP91 is a triple any level positive input to NECL output translator. The device accepts LVPECL, LVTTL, LVCMOS, HSTL, CML or LVDS signals, and translates them to differential NECL output signals (−3.0 V/−5.5 V). To acplish the level translation the EP91 requires three power rails.

MC100EP91 Key Features

- Maximum Input Clock Frequency = > 2.0 GHz Typical

- Maximum Input Data Rate = > 2.0 Gb/s Typical

- 500 ps Typical Propagation Delay

- Operating Range

- Q Output will Default LOW with Inputs Open or at GND

- These Devices are Pb-Free, Halogen Free and are RoHS pliant

- For additional marking information, refer to Application Note AND8002/D

- Rev. 7