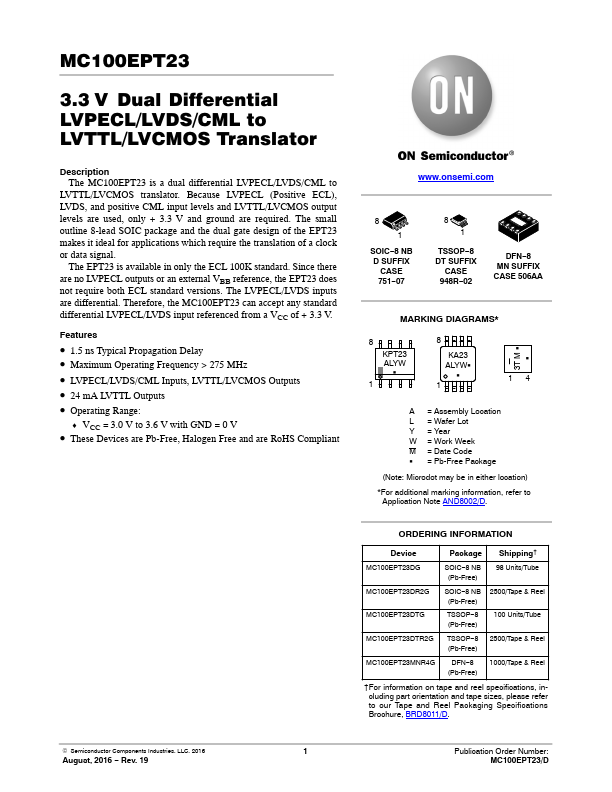

MC100EPT23

Description

The MC100EPT23 is a dual differential LVPECL/LVDS/CML to LVTTL/LVCMOS translator. Because LVPECL (Positive ECL), LVDS, and positive CML input levels and LVTTL/LVCMOS output levels are used, only + 3.3 V and ground are required.

Key Features

- 1.5 ns Typical Propagation Delay

- Maximum Operating Frequency > 275 MHz

- LVPECL/LVDS/CML Inputs, LVTTL/LVCMOS Outputs

- 24 mA LVTTL Outputs

- Operating Range

- VCC = 3.0 V to 3.6 V with GND = 0 V