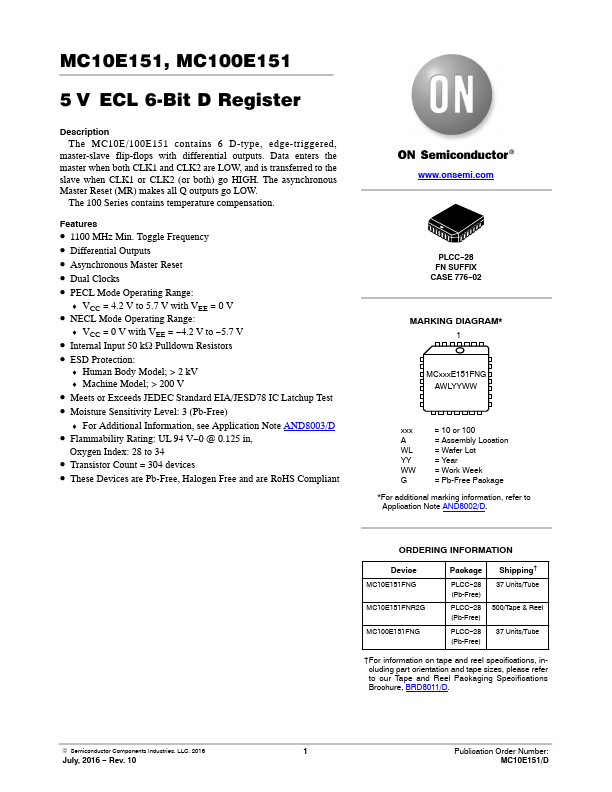

| Part | MC10E151 |

|---|---|

| Description | 6-BIT D REGISTER |

| Manufacturer | onsemi |

| Size | 141.41 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC10E151 | Motorola Semiconductor | 6-BIT D REGISTER |

| MC10E154 | Motorola Semiconductor | 5-BIT 2:1 MUX-LATCH |

| MC10E155 | Motorola Semiconductor | 6-BIT 2:1 MUX-LATCH |

| MC10E150 | Motorola Semiconductor | 6-BIT D LATCH |

| MC10E157 | Motorola Semiconductor | QUAD 2:1 MULTIPLEXER |