MC74AC163 Description

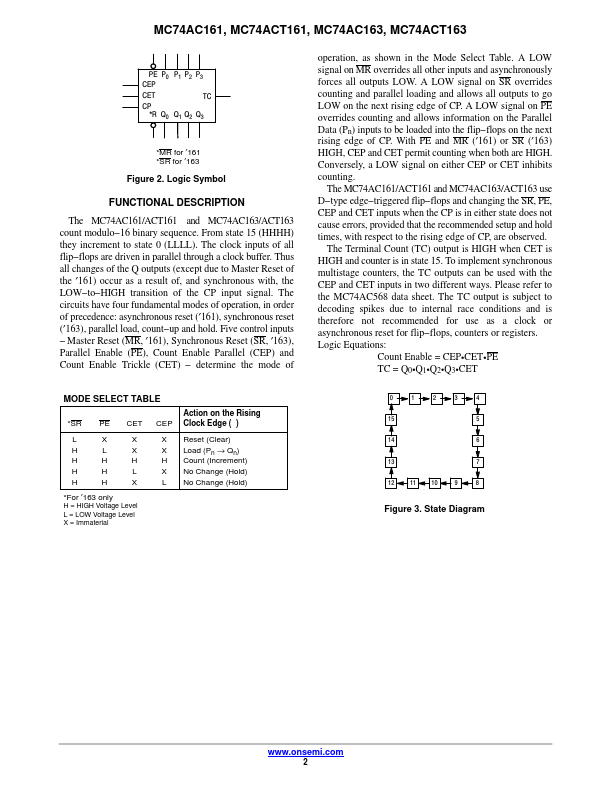

The MC74AC161/ACT161 and MC74AC163/ACT163 count modulo−16 binary sequence. From state 15 (HHHH) they increment to state 0 (LLLL). The clock inputs of all flip−flops are driven in parallel through a clock buffer.

MC74AC163 Key Features

- Synchronous Counting and Loading

- High-Speed Synchronous Expansion

- Typical Count Rate of 125 MHz

- Outputs Source/Sink 24 mA

- These are Pb-Free Devices

- Rev. 8

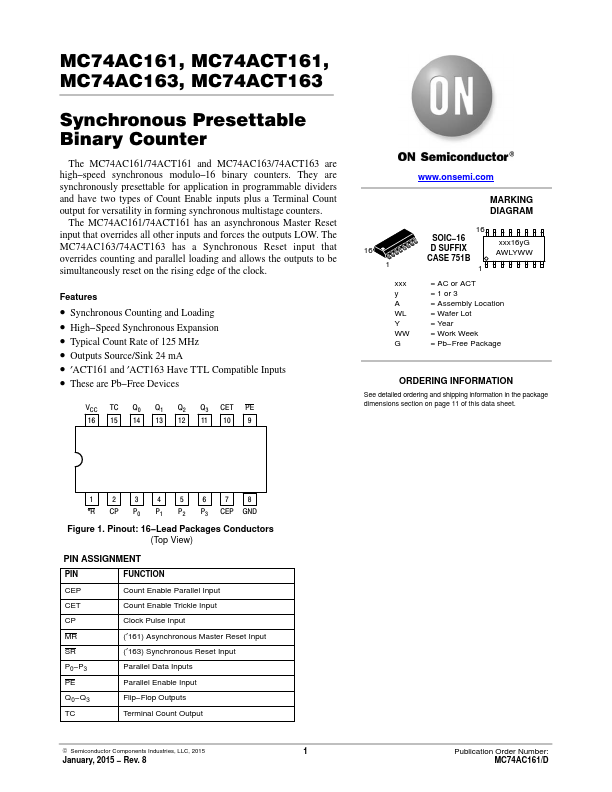

- R Q0 Q1 Q2 Q3

- MR for ′161 -SR for ′163

- Master Reset (MR, ′161), Synchronous Reset (SR, ′163), Parallel Enable (PE), Count Enable Parallel (CEP) and Count Enabl