NL17SHT126 Overview

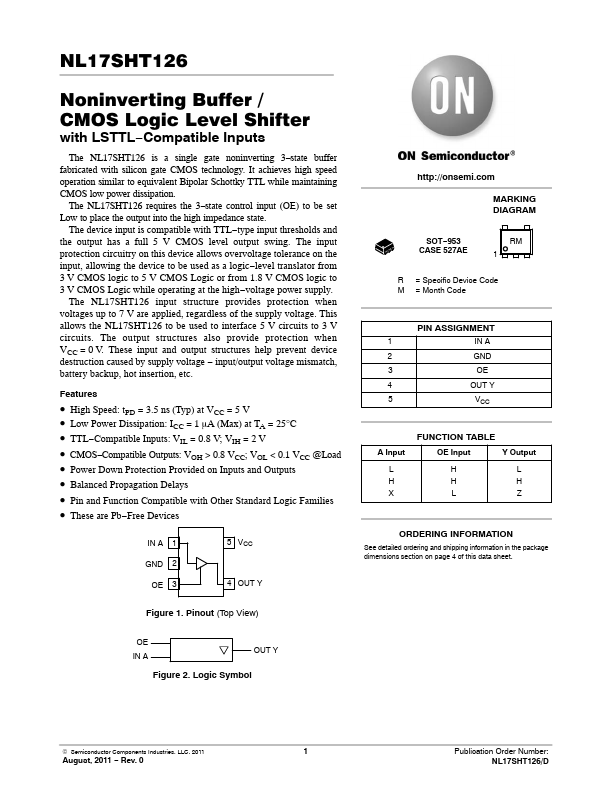

NL17SHT126 Noninverting Buffer / CMOS Logic Level Shifter with LSTTL−patible Inputs The NL17SHT126 is a single gate noninverting 3−state buffer fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation. The NL17SHT126 requires the 3−state control input (OE) to be set Low to place the output into the high...

NL17SHT126 Key Features

- High Speed: tPD = 3.5 ns (Typ) at VCC = 5 V

- Low Power Dissipation: ICC = 1 mA (Max) at TA = 25°C

- TTL-patible Inputs: VIL = 0.8 V; VIH = 2 V

- CMOS-patible Outputs: VOH > 0.8 VCC; VOL < 0.1 VCC @Load

- Power Down Protection Provided on Inputs and Outputs

- Balanced Propagation Delays

- Pin and Function patible with Other Standard Logic Families

- These are Pb-Free Devices

- Rev. 0

- 0.5 to +7.0