PCA9654EA

PCA9654EA is 8-bit I/O Expander manufactured by onsemi.

- Part of the PCA9654E comparator family.

- Part of the PCA9654E comparator family.

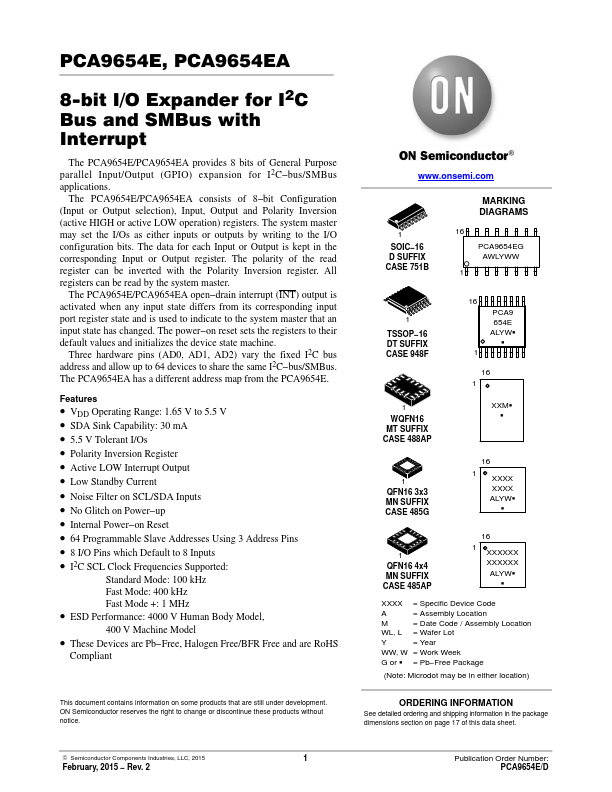

PCA9654E, PCA9654EA

8-bit I/O Expander for I2C Bus and SMBus with Interrupt

The PCA9654E/PCA9654EA provides 8 bits of General Purpose parallel Input/Output (GPIO) expansion for I2C- bus/SMBus applications.

The PCA9654E/PCA9654EA consists of 8- bit Configuration (Input or Output selection), Input, Output and Polarity Inversion (active HIGH or active LOW operation) registers. The system master may set the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each Input or Output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

The PCA9654E/PCA9654EA open- drain interrupt (INT) output is activated when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed. The power- on reset sets the registers to their default values and initializes the device state machine.

Three hardware pins (AD0, AD1, AD2) vary the fixed I2C bus address and allow up to 64 devices to share the same I2C- bus/SMBus. The PCA9654EA has a different address map from the PCA9654E.

Features

- VDD Operating Range: 1.65 V to 5.5 V

- SDA Sink Capability: 30 m A

- 5.5 V Tolerant I/Os

- Polarity Inversion Register

- Active LOW Interrupt Output

- Low Standby Current

- Noise Filter on SCL/SDA Inputs

- No Glitch on Power- up

- Internal Power- on Reset

- 64 Programmable Slave Addresses Using 3 Address Pins

- 8 I/O Pins which Default to 8 Inputs

- I2C SCL Clock Frequencies Supported:

Standard Mode: 100 k Hz Fast Mode: 400 k Hz Fast Mode +: 1 MHz

- ESD Performance: 4000 V Human Body Model,

400 V Machine Model

- These Devices are Pb- Free, Halogen Free/BFR Free and are Ro HS pliant

This document contains information on some products that are still under development. ON Semiconductor reserves the right to change or discontinue these products without notice....