MC100LVELT20 Description

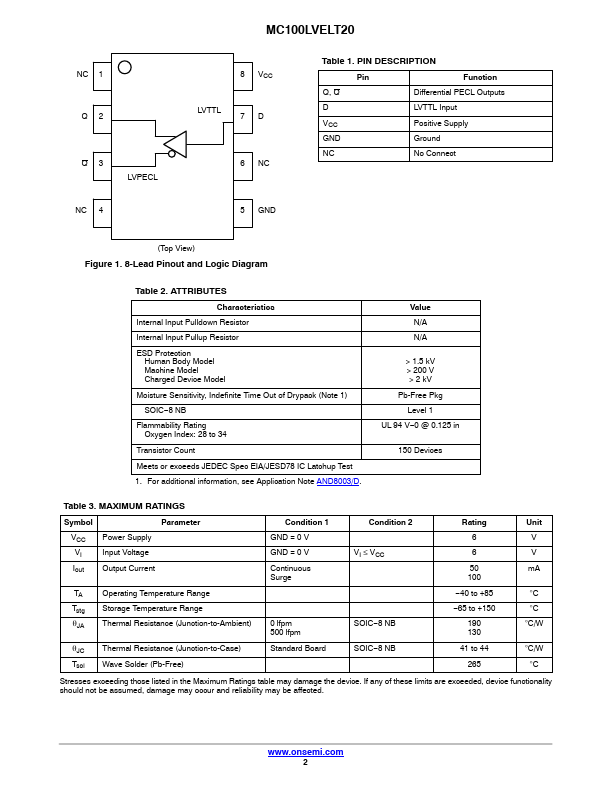

The MC100LVELT20 is a 3.3 V TTL/CMOS to differential PECL translator. Because PECL (Positive ECL) levels are used, only + 3.3 V and ground are required. The small outline SOIC−8 package and the single gate of the MC100LVELT20 makes it ideal for those applications where space, performance, and low power are at a premium.

MC100LVELT20 Key Features

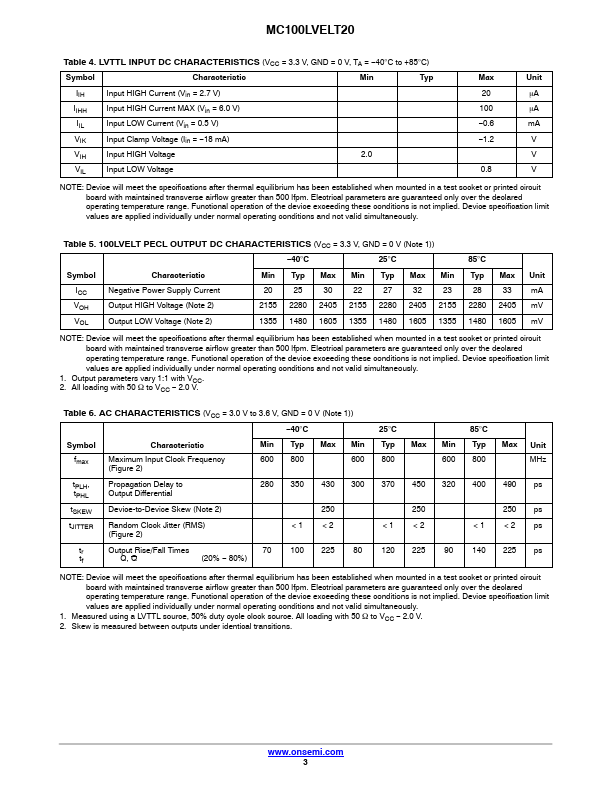

- 390 ps Typical Propagation Delay

- Maximum Input Clock Frequency > 0.8 GHz Typical

- Operating Range VCC = 3.0 V to 3.6 V with GND = 0 V

- PNP TTL Input for Minimal Loading

- Q Output will Default HIGH with Input Open

- These Devices are Pb-Free, Halogen Free and are RoHS pliant

- For additional marking information, refer to Application Note AND8002/