MC74HC112A Description

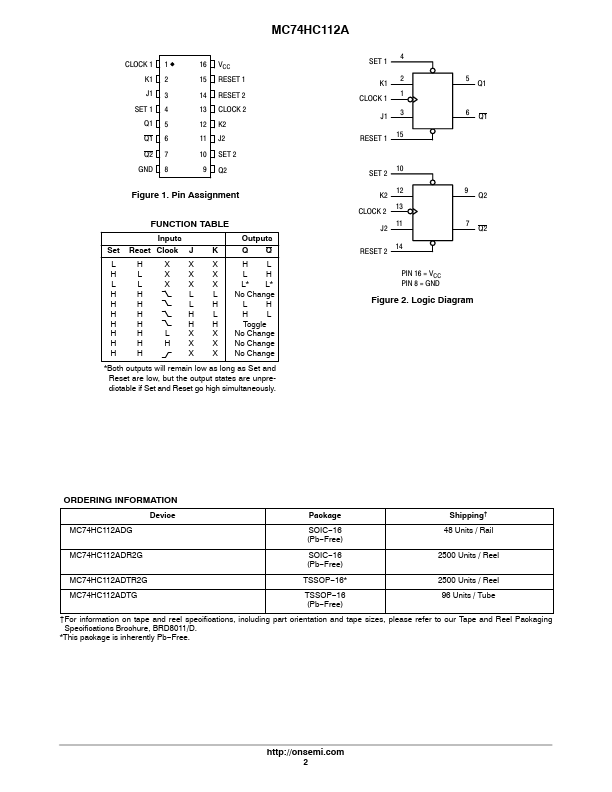

MC74HC112A Dual J-K Flip-Flop with Set and Reset High−Performance Silicon−Gate CMOS The MC74HC112A is identical in pinout to the LS112. The device inputs are patible with standard CMOS outputs; with pullup resistors, they are patible with LSTTL outputs.

MC74HC112A Key Features

- Output Drive Capability: 10 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1.0 mA

- High Noise Immunity Characteristic of CMOS Devices

- In pliance with the Requirements Defined by JEDEC Standard

- Similar in Function to the LS112 Except When Set and Reset are

- Chip plexity: 100 FETs or 25 Equivalent Gates

- These are Pb-Free Devices

- For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering