PCS3P2042B Description

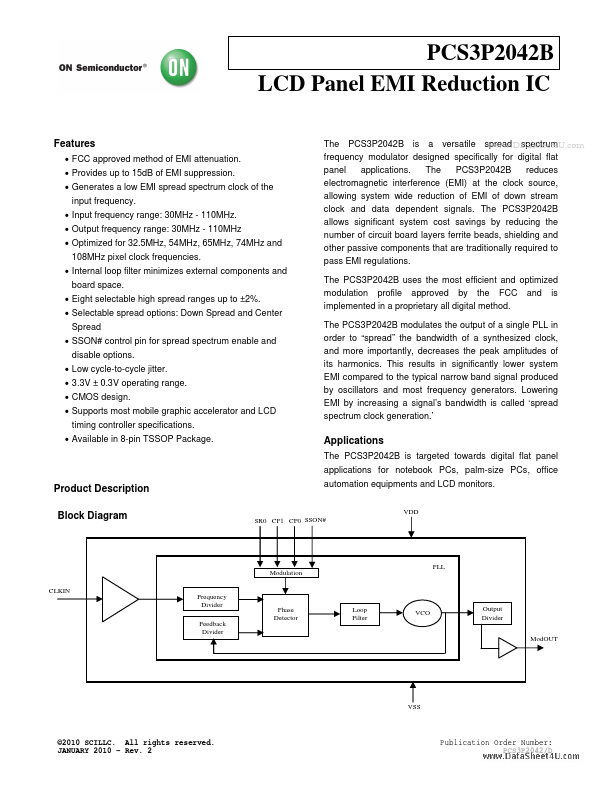

Block Diagram Modulation CLKIN PLL Frequency Divider Feedback Divider Phase Detector Loop Filter VCO Output Divider ModOUT VSS ©2010 SCILLC. 2 Publication Order Number: Connect to externally generated reference signal.

PCS3P2042B Key Features

- FCC approved method of EMI attenuation

- Provides up to 15dB of EMI suppression

- Generates a low EMI spread spectrum clock of the input frequency

- Input frequency range: 30MHz

- 110MHz

- Output frequency range: 30MHz

- 110MHz

- Optimized for 32.5MHz, 54MHz, 65MHz, 74MHz and 108MHz pixel clock frequencies

- Internal loop filter minimizes external ponents and board space

- Eight selectable high spread ranges up to ±2%