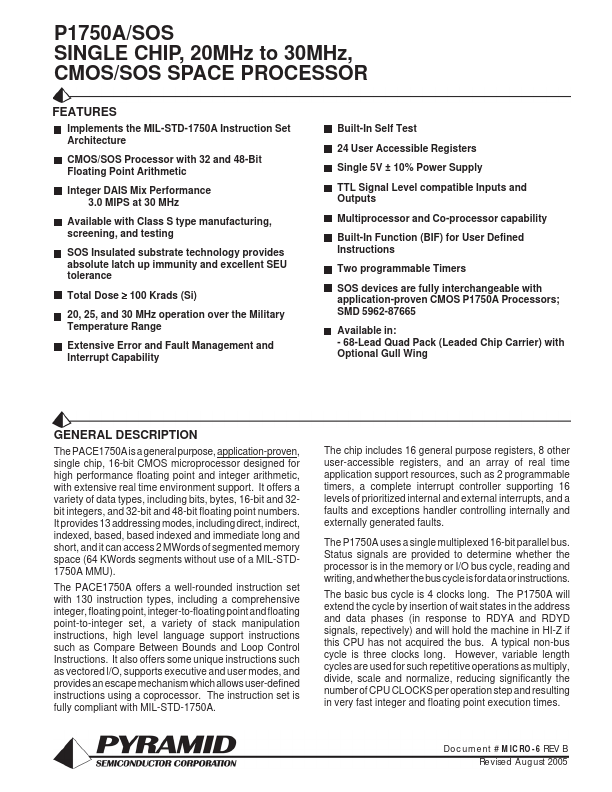

| Part | P1750A-SOS |

|---|---|

| Description | CMOS/SOS SPACE PROCESSOR |

| Manufacturer | PYRAMID |

| Size | 192.19 KB |

Pricing from 202.5 USD, available from Quest.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Quest | 5 | 1+ : 202.5 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| JK-P175 | Jinrui | Polymer PTC Resetable Fuse For Battery Protection |

| P175FP4SNK | Shindengen | Power MOSFET |