P4C187 Overview

Key Specifications

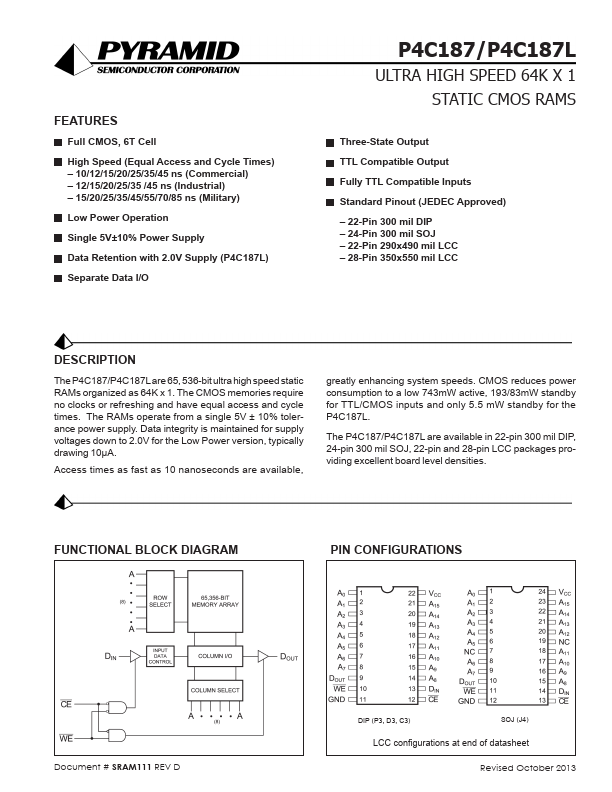

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Description

The P4C187/P4C187Lare 65, 536-bit ultra high speed static RAMs organized as 64K x 1. The CMOS memories require no clocks or refreshing and have equal access and cycle times.