Datasheet Summary

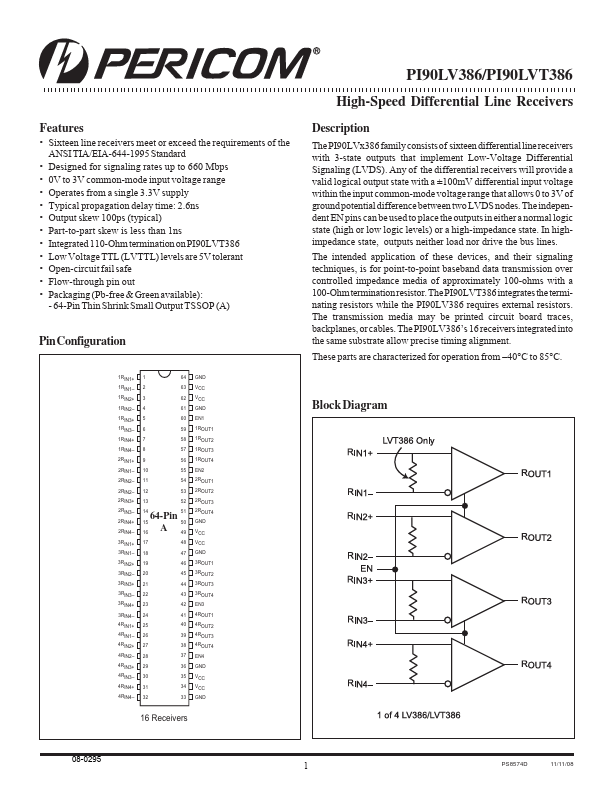

PI90LV386/PI90LVT386

High-Speed Differential Line Receivers

Features

- Sixteen line receivers meet or exceed the requirements of the ANSI TIA/EIA-644-1995 Standard

- Designed for signaling rates up to 660 Mbps

- 0V to 3V mon-mode input voltage range

- Operates from a single 3.3V supply

- Typical propagation delay time: 2.6ns

- Output skew 100ps (typical)

- Part-to-part skew is less than 1ns

- Integrated...