Datasheet Summary

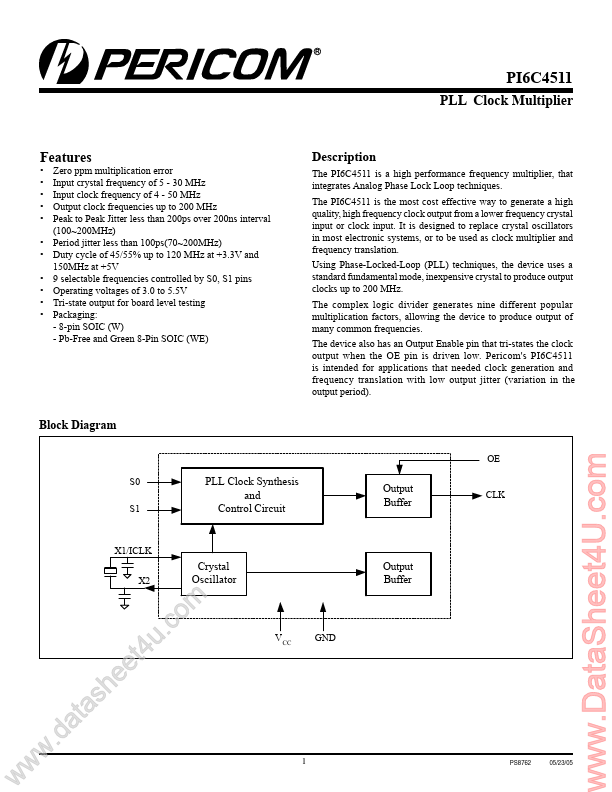

PLL Clock Multiplier

Features

- -

- -

- -

- -

- -

- Zero ppm multiplication error Input crystal frequency of 5

- 30 MHz Input clock frequency of 4

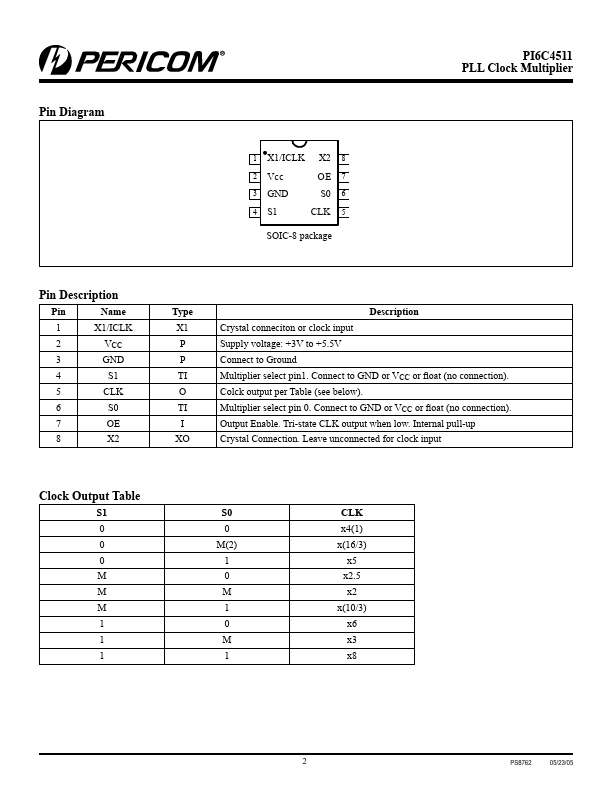

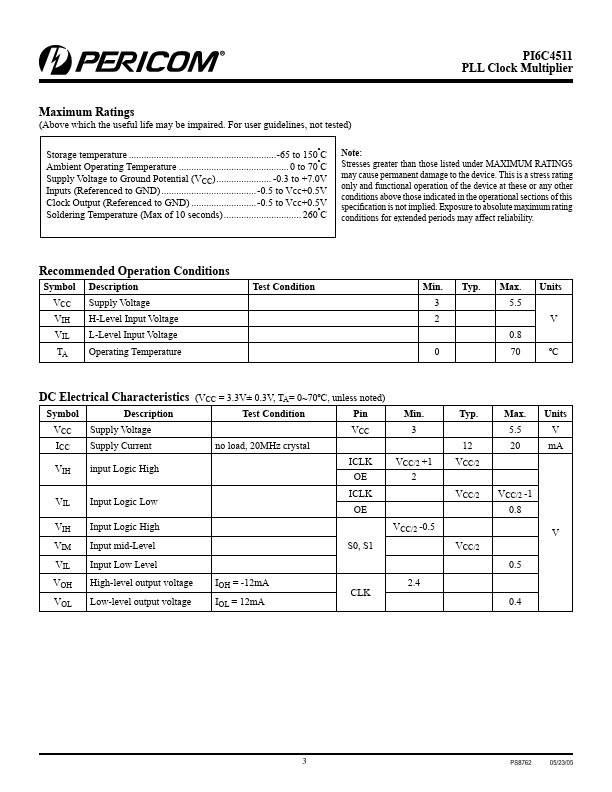

- 50 MHz Output clock frequencies up to 200 MHz Peak to Peak Jitter less than 200ps over 200ns interval (100~200MHz) Period jitter less than 100ps(70~200MHz) Duty cycle of 45/55% up to 120 MHz at +3.3V and 150MHz at +5V 9 selectable frequencies controlled by S0, S1 pins Operating voltages of 3.0 to 5.5V Tri-state output for board level testing Packaging:

- 8-pin SOIC (W)

- Pb-Free and Green 8-Pin SOIC (WE)

Description

The PI6C4511 is a high performance frequency multiplier, that integrates Analog Phase Lock Loop techniques. The...