Datasheet Summary

2.5 GHz 1:4 LVDS Fanout Buffer with Internal Termination

Features

ÎÎFMAX < 2.5GHz ÎÎ4 pairs of differential LVDS outputs ÎÎLow additive jitter, < 0.05ps (max) ÎÎInput CLK accepts: LVDS, LVDS, CML, SSTL input level ÎÎOutput to Output skew: <20ps ÎÎOperating Temperature: -40oC to 85oC ÎÎPower supply: 3.3V ±10% or 2.5V ±5% ÎÎPackaging (Pb-free & Green)

ÎÎ16-pin TQFN available

Description

The PI6C5922504 is a high-performance low-skew 1-to-4 LVDS fanout buffer. The CLK inputs accept LVPECL, LVDS, CML and SSTL signals. PI6C5922504 is ideal for clock distribution applications such as providing fanout for low noise Peri oscillators.

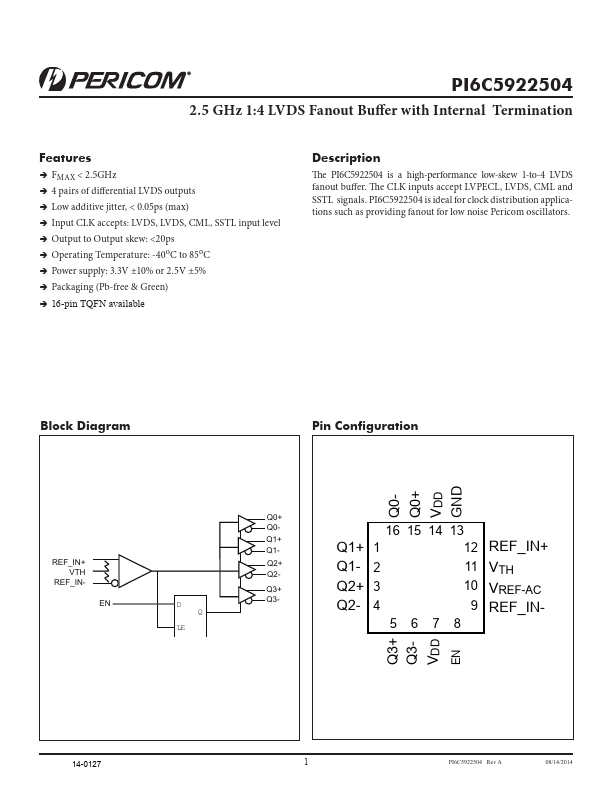

Block Diagram

Pin Configuration

Q0Q0+ VDD...