Datasheet Summary

4 -Output Low Power PCIE GEN 1-2-3 Buffer

Features

ÎÎPhase jitter filter for PCIe 3.0/ 2.0/ 1.0 application ÎÎLow power consumption with independent output power supply 1.8V~3.3V ÎÎLow skew < 60ps ÎÎLow cycle-to-cycle jitter

- 45ps (typ.) @100MHz ÎÎ< 1 ps additive RMS phase jitter ÎÎOutput Enable for all outputs ÎÎProgrammable PLL Bandwidth ÎÎ100 MHz PLL Mode operation ÎÎ1

- 400 MHz Bypass Mode operation ÎÎ3.3V Operation ÎÎPackaging (Pb-free and Green):

-28-Pin TSSOP (L28)

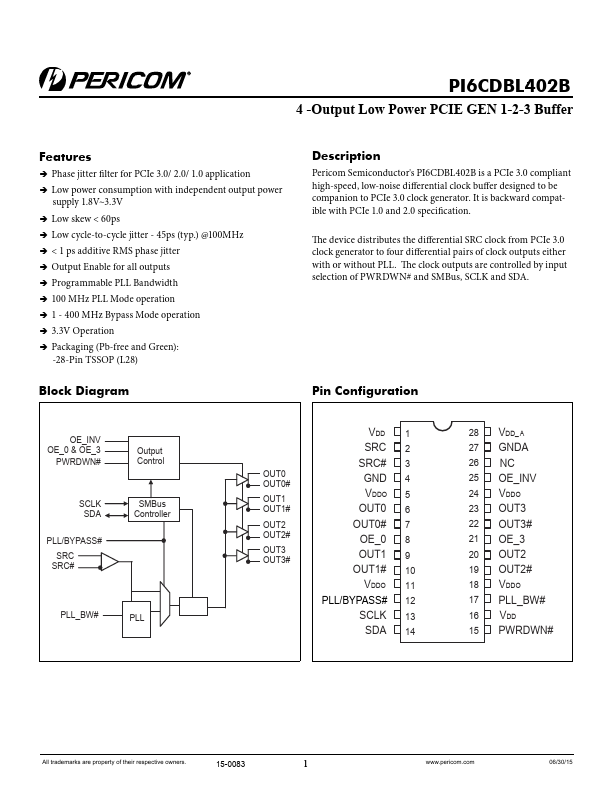

Block Diagram

Description

Peri Semiconductor's PI6CDBL402B is a PCIe 3.0 pliant high-speed, low-noise differential clock buffer designed to be panion to PCIe 3.0 clock generator. It is backward...