PI6LC4820

PI6LC4820 is Ethernet Network Clock Generator manufactured by Pericom Semiconductor.

HiFlexTM Ethernet Network Clock Generator

Features

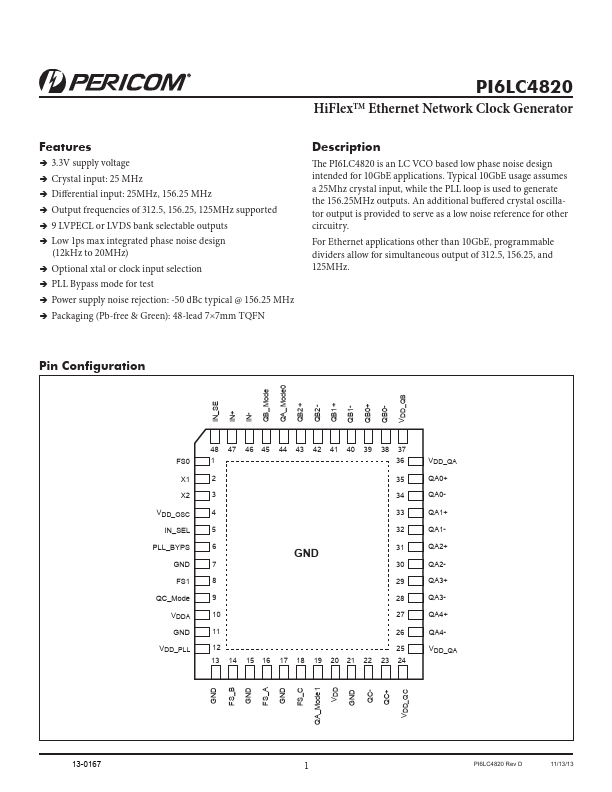

ÎÎ3.3V supply voltage ÎÎCrystal input: 25 MHz ÎÎDifferential input: 25MHz, 156.25 MHz ÎÎOutput frequencies of 312.5, 156.25, 125MHz supported ÎÎ9 LVPECL or LVDS bank selectable outputs ÎÎLow 1ps max integrated phase noise design

(12kHz to 20MHz) ÎÎOptional xtal or clock input selection ÎÎPLL Bypass mode for test ÎÎPower supply noise rejection: -50 dBc typical @ 156.25 MHz ÎÎPackaging (Pb-free & Green): 48-lead 7×7mm TQFN

Description

The PI6LC4820 is an LC VCO based low phase noise design intended for 10GbE applications. Typical 10GbE usage assumes a 25Mhz crystal input, while the PLL loop is used to generate the 156.25MHz...