PI90LV02

PI90LV02 is LVDS High-Speed Differential Line Receiver manufactured by Pericom Semiconductor.

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012 12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PI90LV02/PI90LVT02

SOTiny TM LVDS High-Speed Differential Line Receiver

Features

- Meets or Exceeds the Requirements of ANSI TIA/EIA-644-1995 Standard

- Signaling rates up to 400 Mbps

- Interfaces to LVDS, LVPECL

- Bus-Terminal ESD exceeds 10k V

- Differential Input Voltage Threshold less than 100m V

- Typical Propagation Delay Times of 2.6ns

- Typical Power Dissipation of 40m W @200 MHz

- Low Voltage TTL (LVTTL) Level is 5V Tolerant

- Open-Circuit Fail Safe

- Output are High Impedance with VCC <1.5V

- Integrated 110-ohm Line Termination Resistor (PI90LVT02)

- Operates from a 3.3V supply

- Input mon-mode voltage range 0V- 3.2V

- Industrial Temperature Operating Range:

- 40°C to 85°C

- Packaging (Pb-free & Green available):

- 5-pin space-saving SOT-23 (T)

Description

The PI90LV02 and PI90LVT02 are single differential line receivers that use low-voltage differential signaling (LVDS) to support data rates up to 400 Mbps. These products are designed for applications requiring high-speed, low-power consumption, low-noise generation, and a small package. A differential input signal (350m V) is translated by the device to a 3.3V CMOS output level. The PI90LVT02 integrates the terminating resistor while the PI90LV02 requires an external resistor.

Applications

Applications include point-to-point and multi-drop baseband data transmissions over impedance media of approximately 100-ohms. The transmission media can be printed circuit board traces, backplanes, or cables. The PI90LV02 and PI90LVT02 and panion line drivers (PI90LV01 and PI90LVB01) provide new alternatives to RS-232, PECL, and ECL devices for high-speed, point-to-point interface applications.

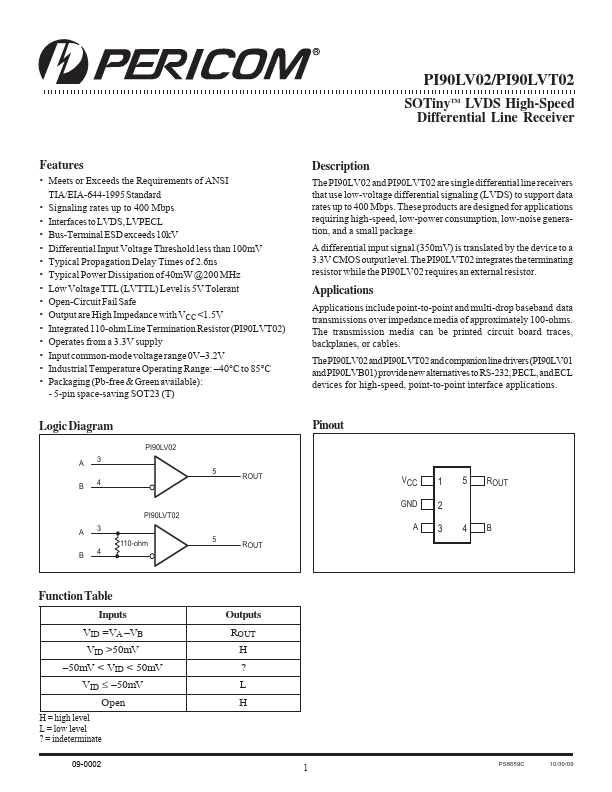

Logic Diagram

PI90LV02 A...